This is an old revision of the document!

Cisco SG220 / SF220 Series

Models

| Model | SoC | PoE | Comment |

|---|---|---|---|

| SG220-26 | RTL8382M | ||

| SG220-26P | RTL8382M | ✓ | |

| SG220-50 | RTL8393M | ||

| SG220-50P | RTL8393M | ✓ | |

| SF220-24 | RTL8332M | 10/100 ports only | |

| SF220-24P | RTL8332M | ✓ | 10/100 ports only |

| SF220-48 | RTL8353M | 10/100 ports only | |

| SF220-48P | RTL8353M | ✓ | 10/100 ports only |

All models share the same firmware image. The image format is the same as the bix format, used by the Zyxel GS1900 series switches.

SG220-26(P)

The SG220-26 and SG220-26P appear to use the same board, although some components related to the PoE management are missing on the SG220-26's main board

- 2× RTL8218B PHYs

- RTL8214FC SFP PHY

- RTL8231 GPIO expander

- 1× MIIM mode (virtual MIIM, address 31)

- 2× Shift register mode (LED_CLK, LED_DAT)

- Winbond W631GU8MB (128MiB DDR3 SDRAM)

- Macronix MX25L25635F, Winbond 25Q256FVFG (32MiB SPI flash)

- Sipex SP3232, ADM3202 RS-232 transceiver

GPIO

- Internal GPIO:

- gpio1: active low, SoC reset

- gpio2: MDC line to RTL8231

- gpio3: MDIO line to RTL8231

- RTL8231 @ phy address 31:

- gpio0-4: device ID

- gpio5-6: device hardware revision

- gpio27: reset button

- gpio16: watchdog state (active low)

- gpio34: (unknown, maybe watchdog related, initialised to 1)

- gpio9: watchdog feed (10s)

- gpio24: SFP25 "OE" (MOD_DEF0?, used to detect module)

- gpio11: SFP25 loss of signal (used to detect media change)/

- gpio17: SFP25 transmit disable

- gpio28: SFP26 "OE" (MOD_DEF0?)

- gpio12: SFP26 loss of signal

- gpio18: SFP26 transmit disable

- gpio15: SCK for SFP25, SFP26, TERM1, TERM2, FAN1, FAN2 (shared I2C clock)

- SDA lines:

- gpio13: SFP25

- gpio14: SFP26

- gpio29: TERM1, TERM2 (26P only)

- gpio31: FAN1 (26P only)

- gpio33: FAN2 (26P only)

Environment

Present only on the SG220-26P.

- FAN1: TC655 at 0x1B. Does not appear to be present on SG220-26P.

- FAN2: TC655 at 0x1B. The TC655 controls both fans behind the PSU of the SG220-26P.

- TEMP1: LM75A at 0x49

- TEMP2: LM75A at 0x4B

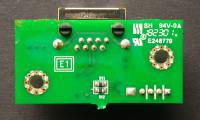

JTAG

The JTAG header uses the MIPS eJTAG pin-out, with pin 12 (key) bound to ground.

- J4.1 TRST#: 1k pull-down

- J4.3 TDI: 10k pull-up

- J4.7 TMS: 10k pull-up

- J4.9 TCK: 10k pull-up

- J4.11 SRST#: 10k pull-up

+-J4-----+

TRST# | 1 2 | GND

TDI | 3 4 | GND

TDO | 5 6 | GND

TMS | 7 8 | GND

TCK | 9 10 | GND

SRST# | 11 12 | GND

N/C | 13 14 | VCC

+--------+