This is an old revision of the document!

Zyxel XGS1210 series

The Zyxel XGS1210 series is a line of managed multi-gigabit Ethernet switches.

| Switch name | gigabit RJ45 ports | multi-gigabit RJ45 | SFP+ ports |

|---|---|---|---|

| XGS1010-12 | 8 | 2 (2.5G/1000M/100M) | 2 |

| XGS1210-12 | 8 | 2 (2.5G/1000M/100M) | 2 |

Architecture Overview

The XGS1210 platform makes use of the various SerDeS units on the RTL9302.

| SDS | Use |

|---|---|

| 2 | RTL8218D |

| 6 | RTL8226 |

| 7 | RTL8226 |

| 8 | SFP+ |

| 9 | SFP+ |

Models

Hardware

- RTL9302B SoC

- Macronix MX25L12833F (16MB flash)

- Nanja NT5CC64M16GP-1 (128MB DDR3 SDRAM)

- RTL8231 GPIO extender to control the port LEDs

- RTL8218D 8x Gigabit PHY

- 2 RTL8226 2.5 Gigabit PHYs

2 Uplink ports are SFP+ cages which support 10GBit Base-X mini GBIC modules.

Power is supplied via a 12V 1.5A standard barrel connector. At the right side behind the grid is UART serial connector. A Serial header can be connected to from the outside of the switch trough the airvents with a standard 2.54mm header. Serial connection is via 115200 baud, 8N1.

Pinout of J5 is from top to bottom:

1 Vcc(3.3V) --\

2 TX --------\ |

3 RX ------\ | |

4 GND ---\ | | |

| | | |

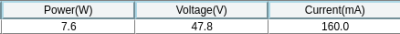

Power consumption

Initial power measurements using a single port, under no load. Measurements are being done by a DGS-1100-8P PoE+ switch

OEM U-Boot shell (without rtk network on) the consumption is 6.0Watts

OEM XGS-1010-12 firmware 7.5Watts

OpenWRT snapshot 7.6Watts

Port & LED numbers

The RTL9302 SoC supports 24 GbE ports, and four 10G ports.

Device ports 1-8 are switch ports 0-7. Device ports 9-12 are switch port 24-27. Ethernet port 1 (eth0) is switch port 28.

| Ports | LED index | LED comment |

|---|---|---|

| 1-8 | 0 | Amber component of Bi-color Amber/Lime-Green LED. LED0 must be off. |

| 1-8 | 1 | Lime-Green component of Bi-color Amber/Lime-Green LED. LED1 must be off. |

| Ports | LED index | LED comment |

| 9-10 | 0 | Multi-LED selection. 0 chooses the Amber/Lime-Green Bi-color LEDs. 1 chooses the RGB LEDs. |

| 9-10 | 1 | LED0 = 0: amber, LED0 = 1: red |

| 9-10 | 2 | LED0 = 0: green, LED0 = 1: green |

| 9-10 | 3 | LED0 = 0: (none), LED0 = 1: blue |

| Ports | LED index | LED comment |

| 11-12 | 0 | Blue |

| 11-12 | 1 | Lime-Green |

Board details

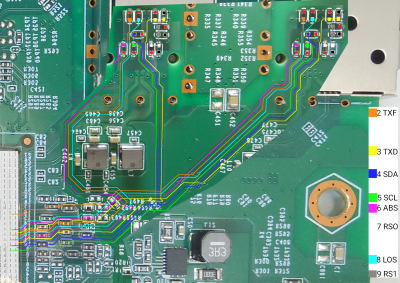

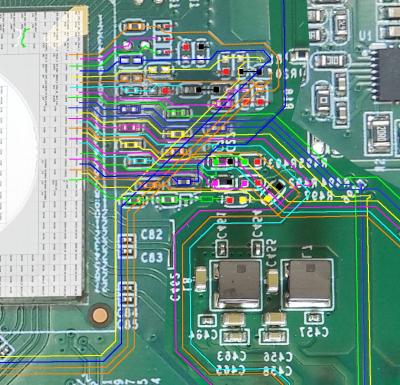

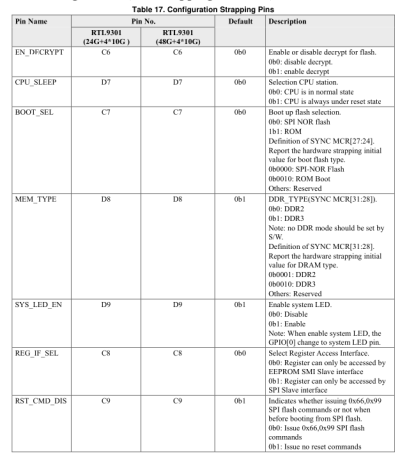

Close up of the strapping pins match what we get from peripherial address 0xb8000100: 0x0080200 0b1000000001000000000. It doesn't tell us what is what however, when looking at https://gitlab.com/olliver/openwrt/realtek_sdk/-/blob/openwrt-dev/loader/u-boot-2011.12/arch/otto40/plr/src/platform/9300/register_map.h#L346 or the datasheet:

XGS1010-12

The XGS1010-12 is identical to the XGS1210-12 in hardware, only the software is different or rather, lack of. The XGS1010-12 contains only the minimal amount of software, to setup and initialize the chips, to actual perform its switching job. While it self-assigns an IP (192.168.1.1), this IP cannot ping or be pinged from Linux. In U-Boot however it can be used after executing rtk network on, to do tftp transfers.

Because the switch is not reachable during normal operation, performing a firmware update is also not possible through this way. The serial port however is available and usable, and can be used to initiate tftpboot or upload software through XYZ-modem variants.

The upside is that due to the very little software on this switch, no configuration data sits there to be corrupted.

NOTE: Buyer beware. While the XGS1010-12 is the identical in hardware _today_, this may not always be the case and cost reductions may lead to smaller flash and smaller RAM chips. While the flash chip is easily replaced, the RAM chip is not. Also, because the switch is not intended to be managed, there is no MAC address provisioned for the switch, bar the SDK hardcoded environment variable Realtek OU part of the MAC address.

OEM Firmware

OEM U-Boot environment

RTL9300# # printenv baudrate=115200 boardmodel=RTL8393M_DEMO bootcmd=boota bootdelay=1 ethaddr=00:E0:4C:00:00:00 ipaddr=192.168.1.1 ledModeInitSkip=0 serverip=192.168.1.111 stderr=serial stdin=serial stdout=serial Environment size: 217/65532 bytes

OEM bootlog

++++ Bootlog |

U-Boot 2011.12.(TRUNK_CURRENT)-svn99721 (Oct 24 2019 - 09:15:40)

Board: RTL9300 CPU:800MHz LX:175MHz DDR:600MHz

DRAM: 128 MB

SPI-F: MXIC/C22018/MMIO16-1/ModeC 1x16 MB (plr_flash_info @ 83f831e4)

Loading 65536B env. variables from offset 0xe0000

*** Warning - bad CRC, using default environment

Net: Net Initialization Skipped

No ethernet found.

Hit Esc key to stop autoboot: 0

## Booting image from partition ... 0

## Booting kernel from Legacy Image at 81000000 ...

Image Name: RTK_SDK

Created: 2019-10-24 9:16:10 UTC

Image Type: MIPS Linux Kernel Image (lzma compressed)

Data Size: 4577343 Bytes = 4.4 MB

Load Address: 80000000

Entry Point: 80283510

Verifying Checksum ... OK

Uncompressing Kernel Image ... OK

Starting kernel ...

console [ttyS0] enabled

bootconsole [early0] disabled

Calibrating delay loop... 531.66 BogoMIPS (lpj=2658304)

pid_max: default: 32768 minimum: 301

Mount-cache hash table entries: 1024 (order: 0, 4096 bytes)

Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes)

NET: Registered protocol family 16

SCSI subsystem initialized

usbcore: registered new interface driver usbfs

usbcore: registered new interface driver hub

usbcore: registered new device driver usb

NET: Registered protocol family 2

TCP established hash table entries: 1024 (order: 0, 4096 bytes)

TCP bind hash table entries: 1024 (order: 2, 20480 bytes)

TCP: Hash tables configured (established 1024 bind 1024)

TCP: reno registered

UDP hash table entries: 256 (order: 1, 12288 bytes)

UDP-Lite hash table entries: 256 (order: 1, 12288 bytes)

NET: Registered protocol family 1

futex hash table entries: 256 (order: 0, 7168 bytes)

msgmni has been set to 239

random: modprobe urandom read with 0 bits of entropy available

io scheduler noop registered

io scheduler deadline registered

io scheduler cfq registered (default)

Serial: 8250/16550 driver, 1 ports, IRQ sharing disabled

serial8250: ttyS0 at MMIO 0x0 (irq = 39, base_baud = 10764700) is a 16550A

RTK_SPI_FLASH_MIO driver is bypassed

RTK_NORSFG3 driver is used

=================================================================

init_luna_nor_spi_map: flash map at 0xb4000000

SPI NOR driver probe...

MXIC/C22018/MMIO16-1/ModeC add SPI NOR partition

MTD partitions obtained from built-in array

Creating 7 MTD partitions on "rtk_norsf_g3":

0x000000000000-0x0000000e0000 : "LOADER"

0x0000000e0000-0x0000000f0000 : "BDINFO"

0x0000000f0000-0x000000100000 : "SYSINFO"

0x000000100000-0x000000200000 : "JFFS2 CFG"

0x000000200000-0x000000300000 : "JFFS2 LOG"

0x000000300000-0x000000980000 : "RUNTIME"

0x000000980000-0x000001000000 : "RUNTIME2"

=================================================================

ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

rtk_gen1_hcd_cs_init: rtk_gen1_hcd_cs_init()!

rtk_gen1_hcd_cs_init: register rtk_gen1_ehci ok!

usb_phy_configure_process: usb_phy_configure_process()!

rtk_gen1-ehci rtk_gen1-ehci: Realtek On-Chip EHCI Host Controller

rtk_gen1-ehci rtk_gen1-ehci: new USB bus registered, assigned bus number 1

rtk_gen1-ehci rtk_gen1-ehci: irq 20, io mem 0x18021000

rtk_gen1-ehci rtk_gen1-ehci: USB 2.0 started, EHCI 1.00

hub 1-0:1.0: USB hub found

hub 1-0:1.0: 1 port detected

usbcore: registered new interface driver usbtmc

usbcore: registered new interface driver usb-storage

TCP: cubic registered

NET: Registered protocol family 17

Freeing unused kernel memory: 3316K (803a3000 - 806e0000)

init started: BusyBox v1.00 (2019.10.23-06:17+0000) multi-call binary

Starting pid 25, console : '/etc/rc'

RTCORE LKM Insert...

allocate mem to rtcore_devices[0].rt_data=0x87c8f000

RTCORE Driver Module Initialize

IOAL init

Log init

Hardware-profile probe (Forced profile: RTL9302B_8218D_2x8226_2xGE)

(RTL9302B_8218D_2x8226_2xGE)

Hardware-profile init

GPIO probe (unit 0): (found)

GPIO Init

Reset PHY gpio OK!

SPI init (unit 0) (type3)

SPI Master init

TC probe (unit 0): (found)

TC init (unit 0)

TC util init (unit 0)

TC util init (isr)

Watchdog probe (unit 0): (found)

Watchdog init (unit 0)

I2C probe (unit 0)

I2C init (unit 0)

RTL8231 probe (unit 0): (found)

RTL8231 init (unit 0)

NIC probe (unit 0)

IOAL init

L2Ntfy probe (unit 0): (found)

RTK Driver Module Initialize

MAC probe (unit 0)

Chip 9302 (found)

MAC init (unit 0)

SMI protocol probe (unit 0)

PHY probe (unit 0)

Chip Construct (unit 0)

Chip Construct

Disable PHY Polling

PHY Reset

MAC Construct

Turn Off Serdes

Serdes Construct

PHY Construct

Turn On Serdes

Enable PHY Polling

Misc

PHY init (unit 0)

Mgmt_dev init (unit 0)

I2C device init (unit 0)

I2C device init (unit 0)

RTNIC Driver Module Initialize

RTDRV Driver Module Initialize

route: not found

RTK.0>

++++

OEM tech-support

++++ sys dump |

RTK.0> sys dump hwp all

Profile Information (C00A86D8):

Profile-Name: RTL9302B_8218D_2x8226_2xGE

Profile-ID: 9300022

Profile-ID-Type: 0

CPU Type: Embedded

SW Desc IDX: 0

Slave Interrupt Pin: 255

Chip count: 1

Cascade Mode: No

unit 0, 9302(1) (cpu)

swcore support: 1

swcore-CPU Interface(1:normal, 2:SPI, 3: PCIe): 1

nic support: 1

port count:13

macId: 0, 1, 2, 3, 4, 5, 6, 7,24,25,26,27,28,

CpuMacId: 28 (attr)

Ether cnt:12, macId(m/M): 0/27 msk:0x0f0000ff 0x00000000 (A)

Uplink cnt: 4, macId(m/M):24/27 msk:0x0f000000 0x00000000 (A)

GE cnt: 8, macId(m/M): 0/ 7 msk:0x000000ff 0x00000000 (E)

2_5GE cnt: 2, macId(m/M): 0/25 msk:0x03000000 0x00000000 (E)

XGE cnt: 2, macId(m/M):26/27 msk:0x0c000000 0x00000000 (E)

Copper cnt:10, macId(m/M): 0/25 msk:0x030000ff 0x00000000 (M)

Serdes cnt: 2, macId(m/M):26/27 msk:0x0c000000 0x00000000 (M)

port: 0, phyIdx0

port: 1, phyIdx0

port: 2, phyIdx0

port: 3, phyIdx0

port: 4, phyIdx0

port: 5, phyIdx0

port: 6, phyIdx0

port: 7, phyIdx0

port:24, phyIdx1

port:25, phyIdx2

port:26, phyIdx255

port:27, phyIdx255

port:28, phyIdx255

PHY Count:3

type:12(8218D ) port:8 baseMac:0

type:19(RTL8226 ) port:1 baseMac:24

type:19(RTL8226 ) port:1 baseMac:25

PHY[0]: chipID 12, baseMacId 0, phy_max 8

PHY[1]: chipID 19, baseMacId 24, phy_max 1

PHY[2]: chipID 19, baseMacId 25, phy_max 1

unitMapStruct[0].pUnitInfo:86c90014,parsed_info=86c90000,swDescp=c00a8724

unitMapStruct[1].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[2].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[3].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[4].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[5].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[6].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[7].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[8].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[9].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[10].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[11].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[12].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[13].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[14].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

unitMapStruct[15].pUnitInfo:c00bbacc,parsed_info=0,swDescp=0

(&parsedInfoEmpty.unitInfo[EMPTY]=c00bbacc)

info->hwp=RTL9302B_8218D_2x8226_2xGE(c00a86d8)

info->hwp_localUnitCnt=1

info->hwp_embeddedCpuUnitId=0

info->hwp_cascade_mode=0

info->hwp_cascadeSlaveUnitID=0

info->hwp->swDescp[0]=c00a8724

info->hwp->swDescp[1]=0

info->hwp->swDescp[2]=0

info->unitInfo[0].hwp_chip_id=93021000

info->unitInfo[0].hwp_chip_revision=1

info->unitInfo[0].hwp_chip_family_id=93000000

info->unitInfo[0].hwp_maxMacId=28

info->unitInfo[0].hwp_minMacId=0

info->unitInfo[0].hwp_macID2PortDescp:

p[0]=c00a8738,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=1,eth=2,medi=1,

p[1]=c00a8748,mac_id=1,phyIdx=0,sdsIdx=0,smi=0,phy_addr=1,attr=1,eth=2,medi=1,

p[2]=c00a8758,mac_id=2,phyIdx=0,sdsIdx=0,smi=0,phy_addr=2,attr=1,eth=2,medi=1,

p[3]=c00a8768,mac_id=3,phyIdx=0,sdsIdx=0,smi=0,phy_addr=3,attr=1,eth=2,medi=1,

p[4]=c00a8778,mac_id=4,phyIdx=0,sdsIdx=0,smi=0,phy_addr=4,attr=1,eth=2,medi=1,

p[5]=c00a8788,mac_id=5,phyIdx=0,sdsIdx=0,smi=0,phy_addr=5,attr=1,eth=2,medi=1,

p[6]=c00a8798,mac_id=6,phyIdx=0,sdsIdx=0,smi=0,phy_addr=6,attr=1,eth=2,medi=1,

p[7]=c00a87a8,mac_id=7,phyIdx=0,sdsIdx=0,smi=0,phy_addr=7,attr=1,eth=2,medi=1,

p[8]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[9]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[10]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[11]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[12]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[13]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[14]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[15]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[16]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[17]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[18]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[19]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[20]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[21]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[22]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[23]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[24]=c00a87b8,mac_id=24,phyIdx=1,sdsIdx=1,smi=1,phy_addr=8,attr=3,eth=4,medi=1,

p[25]=c00a87c8,mac_id=25,phyIdx=2,sdsIdx=2,smi=2,phy_addr=9,attr=3,eth=4,medi=1,

p[26]=c00a87d8,mac_id=26,phyIdx=255,sdsIdx=3,smi=255,phy_addr=255,attr=3,eth=8,medi=8,

p[27]=c00a87e8,mac_id=27,phyIdx=255,sdsIdx=4,smi=255,phy_addr=255,attr=3,eth=8,medi=8,

p[28]=c00a87f8,mac_id=28,phyIdx=255,sdsIdx=255,smi=255,phy_addr=255,attr=8,eth=255,medi=255,

p[29]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[30]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[31]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[32]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[33]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[34]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[35]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[36]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[37]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[38]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[39]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[40]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[41]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[42]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[43]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[44]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[45]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[46]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[47]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[48]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[49]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[50]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[51]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[52]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[53]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[54]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[55]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[56]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[57]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[58]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[59]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[60]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[61]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[62]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

p[63]=c00be0fc,mac_id=0,phyIdx=0,sdsIdx=0,smi=0,phy_addr=0,attr=0,eth=0,medi=0,

info->unitInfo[0].hwp_macID2SerdesID:

p[0]=2,p[1]=2,p[2]=2,p[3]=2,p[4]=2,p[5]=2,p[6]=2,p[7]=2,p[8]=255,p[9]=255,p[10]=255,p[11]=255,p[12]=255,p[13]=255,p[14]=255,p[15]=255,p[16]=255,p[17]=255,p[18]=255,p[19]=255,p[20]=255,p[21]=255,p[22]=255,p[23]=255,p[24]=6,p[25]=7,p[26]=8,p[27]=9,p[28]=255,p[29]=255,p[30]=255,p[31]=255,p[32]=255,p[33]=255,p[34]=255,p[35]=255,p[36]=255,p[37]=255,p[38]=255,p[39]=255,p[40]=255,p[41]=255,p[42]=255,p[43]=255,p[44]=255,p[45]=255,p[46]=255,p[47]=255,p[48]=255,p[49]=255,p[50]=255,p[51]=255,p[52]=255,p[53]=255,p[54]=255,p[55]=255,p[56]=255,p[57]=255,p[58]=255,p[59]=255,p[60]=255,p[61]=255,p[62]=255,p[63]=255,

info->unitInfo[0].hwp_portCpuMacId=28

Ether : count=12, max=27, min=0

Uplink : count=4, max=27, min=24

Cascade: count=0, max=0, min=64

Fe : count=0, max=0, min=64

Ge : count=8, max=7, min=0

Xge : count=2, max=27, min=26

SXge : count=0, max=0, min=64

Copper : count=10, max=25, min=0

Fiber : count=0, max=0, min=64

Combo : count=0, max=0, min=64

Serdes : count=2, max=27, min=26

info->unitInfo[0].hwp_sdsID2phyType:

SDS 2 PHY:12

SDS 6 PHY:19

SDS 7 PHY:19

SDS 8 PHY:20

SDS 9 PHY:20

info->unitInfo[0].hwp_sdsID2MacID:

s[2]=0,s[6]=24,s[7]=25,s[8]=26,s[9]=27,

info->unitInfo[0].hwp_attriPortMask:

attr[0]=f0000ff

attr[0]=0

attr[1]=f000000

attr[1]=0

attr[2]=0

attr[2]=0

attr[3]=10000000

attr[3]=0

attr[4]=0

attr[4]=0

info->unitInfo[0].hwp_ethTypePortMask:

eth[0]=0

eth[0]=0

eth[1]=ff

eth[1]=0

eth[2]=3000000

eth[2]=0

eth[3]=c000000

eth[3]=0

eth[4]=0

eth[4]=0

info->unitInfo[0].hwp_mediumPortMask:

med[0]=30000ff

med[0]=0

med[1]=0

med[1]=0

med[2]=0

med[2]=0

med[3]=c000000

med[3]=0

info->unitInfo[0].hwp_allPortMask=1f0000ff

info->unitInfo[0].hwp_allPortMask=0

info->unitInfo[0].hwp_macID2phyAddr:

p[0]=0,p[1]=1,p[2]=2,p[3]=3,p[4]=4,p[5]=5,p[6]=6,p[7]=7,p[8]=255,p[9]=255,p[10]=255,p[11]=255,p[12]=255,p[13]=255,p[14]=255,p[15]=255,p[16]=255,p[17]=255,p[18]=255,p[19]=255,p[20]=255,p[21]=255,p[22]=255,p[23]=255,p[24]=8,p[25]=9,p[26]=255,p[27]=255,p[28]=255,p[29]=255,p[30]=255,p[31]=255,p[32]=255,p[33]=255,p[34]=255,p[35]=255,p[36]=255,p[37]=255,p[38]=255,p[39]=255,p[40]=255,p[41]=255,p[42]=255,p[43]=255,p[44]=255,p[45]=255,p[46]=255,p[47]=255,p[48]=255,p[49]=255,p[50]=255,p[51]=255,p[52]=255,p[53]=255,p[54]=255,p[55]=255,p[56]=255,p[57]=255,p[58]=255,p[59]=255,p[60]=255,p[61]=255,p[62]=255,p[63]=255,

info->unitInfo[0].hwp_macID2phyType:

p[0]=12,p[1]=12,p[2]=12,p[3]=12,p[4]=12,p[5]=12,p[6]=12,p[7]=12,p[8]=27,p[9]=27,p[10]=27,p[11]=27,p[12]=27,p[13]=27,p[14]=27,p[15]=27,p[16]=27,p[17]=27,p[18]=27,p[19]=27,p[20]=27,p[21]=27,p[22]=27,p[23]=27,p[24]=19,p[25]=19,p[26]=20,p[27]=20,p[28]=20,p[29]=27,p[30]=27,p[31]=27,p[32]=27,p[33]=27,p[34]=27,p[35]=27,p[36]=27,p[37]=27,p[38]=27,p[39]=27,p[40]=27,p[41]=27,p[42]=27,p[43]=27,p[44]=27,p[45]=27,p[46]=27,p[47]=27,p[48]=27,p[49]=27,p[50]=27,p[51]=27,p[52]=27,p[53]=27,p[54]=27,p[55]=27,p[56]=27,p[57]=27,p[58]=27,p[59]=27,p[60]=27,p[61]=27,p[62]=27,p[63]=27,

info->unitInfo[0].hwp_sdsID2SerdesDescp:

sds[0]=c00be0f8,sds[1]=c00be0f8,sds[2]=c00a8b39,sds[3]=c00be0f8,sds[4]=c00be0f8,sds[5]=c00be0f8,sds[6]=c00a8b3b,sds[7]=c00a8b3d,sds[8]=c00a8b3f,sds[9]=c00a8b41,sds[10]=c00be0f8,sds[11]=c00be0f8,sds[12]=c00be0f8,sds[13]=c00be0f8,sds[14]=c00be0f8,sds[15]=c00be0f8,sds[16]=c00be0f8,sds[17]=c00be0f8,sds[18]=c00be0f8,sds[19]=c00be0f8,sds[20]=c00be0f8,sds[21]=c00be0f8,sds[22]=c00be0f8,sds[23]=c00be0f8,

info->unitInfo[0].hwp_phyBaseMacID:

p[0]=0,p[1]=0,p[2]=0,p[3]=0,p[4]=0,p[5]=0,p[6]=0,p[7]=0,p[8]=255,p[9]=255,p[10]=255,p[11]=255,p[12]=255,p[13]=255,p[14]=255,p[15]=255,p[16]=255,p[17]=255,p[18]=255,p[19]=255,p[20]=255,p[21]=255,p[22]=255,p[23]=255,p[24]=24,p[25]=25,p[26]=26,p[27]=27,p[28]=28,p[29]=255,p[30]=255,p[31]=255,p[32]=255,p[33]=255,p[34]=255,p[35]=255,p[36]=255,p[37]=255,p[38]=255,p[39]=255,p[40]=255,p[41]=255,p[42]=255,p[43]=255,p[44]=255,p[45]=255,p[46]=255,p[47]=255,p[48]=255,p[49]=255,p[50]=255,p[51]=255,p[52]=255,p[53]=255,p[54]=255,p[55]=255,p[56]=255,p[57]=255,p[58]=255,p[59]=255,p[60]=255,p[61]=255,p[62]=255,p[63]=255,

info->unitInfo[0].hwp_ledNum:

p[0]=2,p[1]=2,p[2]=2,p[3]=2,p[4]=2,p[5]=2,p[6]=2,p[7]=2,p[8]=0,p[9]=0,p[10]=0,p[11]=0,p[12]=0,p[13]=0,p[14]=0,p[15]=0,p[16]=0,p[17]=0,p[18]=0,p[19]=0,p[20]=0,p[21]=0,p[22]=0,p[23]=0,p[24]=4,p[25]=4,p[26]=2,p[27]=2,p[28]=255,p[29]=0,p[30]=0,p[31]=0,p[32]=0,p[33]=0,p[34]=0,p[35]=0,p[36]=0,p[37]=0,p[38]=0,p[39]=0,p[40]=0,p[41]=0,p[42]=0,p[43]=0,p[44]=0,p[45]=0,p[46]=0,p[47]=0,p[48]=0,p[49]=0,p[50]=0,p[51]=0,p[52]=0,p[53]=0,p[54]=0,p[55]=0,p[56]=0,p[57]=0,p[58]=0,p[59]=0,p[60]=0,p[61]=0,p[62]=0,p[63]=0,

info->unitInfo[0].hwp_multiSdsPortSdsmask:

info->unitInfo[0].hwp_multiSdsBaseSds:

info->unitInfo[0].hwp_macID2SCDescp:

info->unitInfo[0].hwp_scBaseMacID:

info->unitInfo[0].swDescp=c00a8724

info->unitInfo[0].parsed_info=86c90000

++++

By tftpbooting the XGS1210-12 `.bix` file, we get into the Zylinx shell, which while restrictive, allows us to do `show tech-support`.

Board GPIO

Device Pin Direction Default Current Purpose ------- ---- ---------- -------- -------- -------- INT 0 OUT 0 0 SYSTEM-LED INT 1 N/A Not Connected INT 2 N/A Not Connected SPI 3 N/A Goes to unpopluated U23 (SPI_CLK) SPI 4 N/A Goes to unpopluated U23 (SPI_MISO) SPI 5 N/A Goes to unpopluated U23 (SPI_MOSI) INT 6 IN 0 0 Permanently Pulled down, likely to indicate presence of U23 INT 7 IN 1 1 Permanently Pulled up, likely to indicate presence of ...? I2C 8 OUT Shared SFP clock (SFP0/SFP1: SCK) Pull-up near SFP0 I2C 9 I/O SDA0: (SFP0_SDA) Pull-up near SFP0 I2C 10 I/O SDA1: (SFP1_SDA) Pull-up near SFP1 INT 11 OUT 0 0 Transmit Disable (SFP0: TX_DIS_FX) Pull-up near SFP0 INT 12 IN 0 0 Absent detection (SFP0: MOD-DEF0) Pull-up near SFP0 INT 13 IN 0 0 Los of Signal (SFP0: LOS) Pull-up near SFP0 (pull down NP option) INT 14 IN 0 0 Transmit Fault (SFP0: TX_FAULT) Pull-up near SFP0 INT 15 OUT 0 0 Transmit Disable (SFP1: TX_DIS_FX) Pull-up near SFP1 INT 16 IN 0 0 Absent detection (SFP1: MOD-DEF0) Pull-up near SFP1 INT 17 IN 0 0 Los of Signal (SFP1: LOS) Pull-up near SFP1 (pull down NP option) INT 18 IN 0 0 Permanently pulled down? Trace not found ... INT 19 IN 0 0 Permanently pulled down? Trace not found ... INT 20 OUT 0 0 Goes to U10? INT 21 IN 0 0 Transmit Fault (SFP1: TX_FAULT) Pull-up near SFP1 INT 22 OUT 1 1 Reset_PHY? INT 23 IN Reset Button

Note, that RS0/RS1 for both SFP's have permanent pull-ups, but also have the pull-down option. Not connected/lost traces can still exist on an internal layer (Reset for example).

USB

While this switch has no USB ports, the USB pins appear to be on TP2 and TP3 on the bottom (to be confirmed)

The OEM OS boots into the Realtek SDK diag application, which can be exited with exit to get dropped into a Busybox shell. Because the switch is not managed, no network initialization happens, making for a pretty fast boot.

OEM Flash layout

U-Boot

RTL9300# # flshow =============== FLASH Partition Layout =============== Index Name Size Address ------------------------------------------------------ 0 LOADER 0xe0000 0xb4000000-0xb40dffff 1 BDINFO 0x10000 0xb40e0000-0xb40effff 2 SYSINFO 0x10000 0xb40f0000-0xb40fffff 3 JFFS2_CFG 0x100000 0xb4100000-0xb41fffff 4 JFFS2_LOG 0x100000 0xb4200000-0xb42fffff 5 RUNTIME1 0x680000 0xb4300000-0xb497ffff 6 RUNTIME2 0x680000 0xb4980000-0xb4ffffff ======================================================

Linux

# cat /proc/mtd dev: size erasesize name mtd0: 000e0000 00001000 "LOADER" mtd1: 00010000 00001000 "BDINFO" mtd2: 00010000 00001000 "SYSINFO" mtd3: 00100000 00001000 "JFFS2 CFG" mtd4: 00100000 00001000 "JFFS2 LOG" mtd5: 00680000 00001000 "RUNTIME" mtd6: 00680000 00001000 "RUNTIME2"

OEM U-Boot Self-test failure

============= Factory Test Begin ============= HTP log info get: htpModeIf=1, htpBreakIf=0, hour=20, entry=12800, round=808859448 ! HTP Test log full! ============= Factory Test End ! =============

The OEM bootloader (U-Boot 2011.12.(TRUNK_CURRENT)-svn99721 (Oct 24 2019 - 09:15:40)) runs a self-check upon startup. This check byte is in the middle of the flash, stored at address `0x810000` (just beyond the 8MiB marker) on the XGS1010-12. With the recently new introduced mtd-concat, we can however define two regions and concatate those logically in Linux. The upside is, unless Zyxel recompiled their firmware (unnecessary work for them, but possible), using a smaller flash-chip would be less-likely.

As an alternative, the XGS1210-12 U-Boot binary can be flashed, which turns the XGS1010-12 'more' into a XGS1210-12, which puts this self-check at the end of the flash.

References

XGS1210-12

OEM Firmware

It ships with a u-boot bootloader (U-Boot Version V1.0.0.1 (Oct 14 2019 - 17:51:23)) based on Realtek's SDK for RTL93xx SoCs and Linux 3.18 based on Realtek's SDK 3.x. It has a web interface for all management functions.

OpenWRT Bootlog

++++ Full OpenWRT Bootlog |

Board: RTL9300 CPU:800MHz LX:175MHz DDR:600MHz

DRAM: 128 MB

SPI-F: MXIC/C22018/MMIO16-1/ModeC 1x16 MB (plr_flash_info @ 83f6a2a4)

Loading 65536B env. variables from offset 0xe0000

Net: Net Initialization Skipped

No ethernet found.

Hit Esc key to stop autoboot: 0

RTL9300# # rtk network on

Enable network

RTCORE Driver Module Initialize

IOAL init

Hardware-profile probe GPIO probe (unit 0): (found)

GPIO Init

RTL8231 probe (unit 0): (found)

RTL8231 init (unit 0)

(XGS1210_12)

Hardware-profile init

GPIO probe (unit 0): (found)

GPIO Init rtl9300_gpio_init had already been initialized!

SPI init (unit 0)

I2C probe (unit 0)

I2C init (unit 0)

RTL8231 probe (unit 0): (found)

RTL8231 init (unit 0)

r9300_rtl8231_init had already been initialized!

NIC probe (unit 0)

Loader RTNIC Driver Module Initialize

IOAL init

RTK Driver Module Initialize

MAC probe (unit 0)

Chip 9302 (found)

MAC init (unit 0)

SMI protocol probe (unit 0)

PHY probe (unit 0)

Chip Construct (unit 0)

Chip Construct

Disable PHY Polling

PHY Reset

MAC Construct

Turn Off Serdes

Serdes Construct

PHY Construct

Turn On Serdes

Enable PHY Polling

Misc

PHY init (unit 0)

Mgmt_dev init (unit 0)

Please wait for PHY init-time ...

RTL9300# # run loadcmd

Using rtl9300#0 device

TFTP from server 192.168.1.150; our IP address is 192.168.1.1

Filename 'openwrt-rtl838x-zyxel_xgs1210-12-initramfs-kernel.bin'.

Load address: 0x84f00000

Loading: #################################################################

#################################################################

#################################################################

#################################################################

#################################################################

#################################################################

###########################

done

Bytes transferred = 6110544 (5d3d50 hex)

RTL9300# # bootm

## Booting kernel from Legacy Image at 84f00000 ...

Image Name: OpenWRT

Created: 2020-12-02 18:53:07 UTC

Image Type: MIPS Linux Kernel Image (gzip compressed)

Data Size: 6110480 Bytes = 5.8 MB

Load Address: 80220000

Entry Point: 80220000

Verifying Checksum ... OK

Uncompressing Kernel Image ... OK

Starting kernel ...

[ 0.000000] Linux version 5.4.70 (birger@AMDDesktop) (gcc version 8.4.0 (OpenWrt GCC 8.4.0 r14727-627da9a38c)) #0 Wed Dec 2 18:53:07 2020

[ 0.000000] prom_init called

[ 0.000000] RTL838X model is 0

[ 0.000000] RTL839X model is 0

[ 0.000000] RTL93XX model is 93021001

[ 0.000000] SoC Type: RTL9302

[ 0.000000] Kernel command line:

[ 0.000000] printk: bootconsole [early0] enabled

[ 0.000000] CPU0 revision is: 00019555 (MIPS 34Kc)

[ 0.000000] plat_mem_setup called

[ 0.000000] MIPS: machine is Zyxel XGS1210-12 Switch

[ 0.000000] Registering _machine_restart

[ 0.000000] NO PCI device found

[ 0.000000] Initrd not found or empty - disabling initrd

[ 0.000000] device_tree_init called

[ 0.000000] Using appended Device Tree.

[ 0.000000] Primary instruction cache 32kB, VIPT, 4-way, linesize 32 bytes.

[ 0.000000] Primary data cache 32kB, 4-way, PIPT, no aliases, linesize 32 bytes

[ 0.000000] Zone ranges:

[ 0.000000] Normal [mem 0x0000000000000000-0x0000000007ffffff]

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000000000000-0x0000000007ffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000000000000-0x0000000007ffffff]

[ 0.000000] On node 0 totalpages: 32768

[ 0.000000] Normal zone: 288 pages used for memmap

[ 0.000000] Normal zone: 0 pages reserved

[ 0.000000] Normal zone: 32768 pages, LIFO batch:7

[ 0.000000] pcpu-alloc: s0 r0 d32768 u32768 alloc=1*32768

[ 0.000000] pcpu-alloc: [0] 0

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 32480

[ 0.000000] Kernel command line: console=ttyS0,115200

[ 0.000000] Dentry cache hash table entries: 16384 (order: 4, 65536 bytes, linear)

[ 0.000000] Inode-cache hash table entries: 8192 (order: 3, 32768 bytes, linear)

[ 0.000000] Writing ErrCtl register=00028d08

[ 0.000000] Readback ErrCtl register=00028d08

[ 0.000000] mem auto-init: stack:off, heap alloc:off, heap free:off

[ 0.000000] Memory: 114836K/131072K available (4762K kernel code, 168K rwdata, 1060K rodata, 8724K init, 199K bss, 16236K reserved, 0K cma-reserved)

[ 0.000000] SLUB: HWalign=32, Order=0-3, MinObjects=0, CPUs=1, Nodes=1

[ 0.000000] NR_IRQS: 64

[ 0.000000] Found Interrupt controller: cpuintc (cpuintc)

[ 0.000000] ICU Memory: b8003000

[ 0.000000] random: get_random_bytes called from start_kernel+0x32c/0x518 with crng_init=0

[ 0.000000] CPU frequency from device tree: 700000000

[ 0.000000] CPU Clock: 700 MHz

[ 0.000000] PLL control register: 0

[ 0.000000] Found NS16550a: uart (uart@b8002000)

[ 0.000000] Using default baud rate: 38400

[ 0.000000] clocksource: MIPS: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 5460744132 ns

[ 0.000008] sched_clock: 32 bits at 350MHz, resolution 2ns, wraps every 6135667710ns

[ 0.009618] printk: console [ttyS0] enabled

[ 0.009618] printk: console [ttyS0] enabled

[ 0.020076] printk: bootconsole [early0] disabled

[ 0.020076] printk: bootconsole [early0] disabled

++++

OpenWrt Support

There is experimental OpenWrt support: the device boots and the Ethernet and switch driver function. The 1 and 2.5 GBit ports work, but not the SFP+ cages. No GPIO support so far.