Hasivo S1100WP-8GT_SE

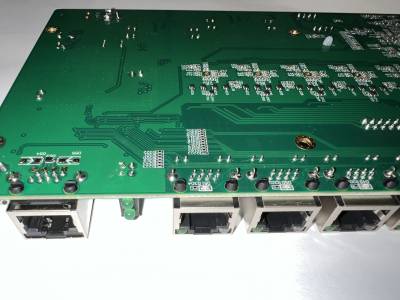

The S1100WP-8GT_SE is an 8-port Multi-Gigabit L3 switch. It has 8 2.5GbE ports, and supports 802.3af/at on all ports, alongside 802.3bt on Port 1 out of the box. PoE is provided by a pair of HS104PTI chips, which are capable of supporting 802.3bt (90W) on each port.. however hardware constraints including trace thickness would be a limit (hence why 802.3bt defaults to port 1, shortest trace length)

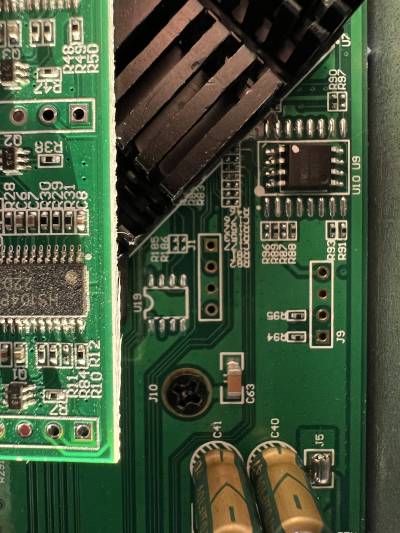

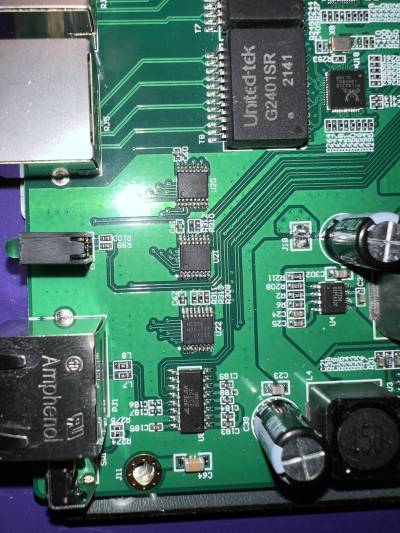

Hardware

- RTL9303 SoC

- Fudan FM25Q128A QSPI (16MB flash) 2201121400_fudan-micro-fm25q128a-sob-u-g_c2928936.pdf

- Samsung K4B2G1646F-BYMA (256MB DDR3 SDRAM)

- 3x HC595 shift registers for the port LEDs (Link + Activity)

- 1x 8051 MCU STC8G1K08 responsible for PoE / Fan interactions (controls PoE LEDs and fan PWM)

- 8× 2.5GbE via individual RTL8221B PHYs

Power is supplied via a 52V barrel connector.

Default Config

Out of the box configuration is:

- IP: 192.168.0.1

- Subnet: 255.255.255.0

- TFTP server: 192.168.0.111

PoE config:

- Port 1: 802.3bt

- Port 2: 802.3at

- Port 3: 802.3at

- Port 4: 802.3at

- Port 5: 802.3at

- Port 6: 802.3at

- Port 7: 802.3at

- Port 8: 802.3at

Uboot Password

ESC during Uboot to enter password prompt Password is 'Hs2021cfgmg'

IO mapping

SoC

| Pin(s) | GPIO | Alt Func | Description |

|---|---|---|---|

| B1/B2 | n/a | UART0_TXD/UART0_RXD | UART0 Tx/Rx to RS232 transceiver for console port |

| B5 | GPIO0 | n/a | SYS LED (Green) |

| A14 | GPIO19 | n/a | LED HC595 RCLK Output |

| A16 | GPIO23 | n/a | ???, has internal pulldown, but reads high when idle |

| AG23,AF23,AG25,AF25 | n/a | HSOP_S2,HSON_S2,HSIP_S2,HSIN_S2 | SerDes 2 to RTL8221B Port 0 PHY |

| AD26,AD27,AB26,AB27 | n/a | HSOP_S3,HSON_S3,HSIP_S3,HSIN_S3 | SerDes 3 to RTL8221B Port 8 PHY |

| V27,V26,T27,T26 | n/a | HSOP_S4,HSON_S4,HSIP_S4,HSIN_S4 | SerDes 4 to RTL8221B Port 16 PHY |

| P26,P27,M26,M27 | n/a | HSOP_S5,HSON_S5,HSIP_S5,HSIN_S5 | SerDes 5 to RTL8221B Port 20 PHY |

| K27,K26,H27,H26 | n/a | HSOP_S6,HSON_S6,HSIP_S6,HSIN_S6 | SerDes 6 to RTL8221B Port 24 PHY |

| F26,F27,D26,D27 | n/a | HSOP_S7,HSON_S7,HSIP_S7,HSIN_S7 | SerDes 7 to RTL8221B Port 25 PHY |

| A25,B25,A23,B23 | n/a | HSOP_S8,HSON_S8,HSIP_S8,HSIN_S8 | SerDes 8 to RTL8221B Port 26 PHY |

| B21,A21,B19,A19 | n/a | HSOP_S9,HSON_S9,HSIP_S9,HSIN_S9 | SerDes 9 to RTL8221B Port 27 PHY |

| E2,H1,H2,G2,G1,F2,F1 | n/a | SPI_MST_CS[0], SPI_MST_… | SPI Master Interface to Flash Memory |

| AD23,AE24 | n/a | M0_MDC,M0_MDIO | MDIO 0 Interface to [1]PHY0,[2]PHY8,[3]PHY16,[4]PHY20 |

| AG27,AF27 | n/a | M1_MDC,M1_MDIO | MDIO 1 Interface to [1]PHY24,[2]PHY25,[3]PHY26,[4]PHY27 |

| N1,U2,M2,U1,M1,V1,N2,V2,AA1,K1,Y2,J2,Y1,K2,W2,L1 | n/a | MD[15:0] | DDR3 SDRAM Data Input/Output |

| AE8,AE1,AF4,AF1,AD2,AB1,AG4,AD1,AG5,AC2,AF6,AC1,AG6,AG3,AE2,AF3 | n/a | MA[15:0] | DDR3 SDRAM Address Outputs |

| AG2,AB2,AF7 | n/a | BA[2:0] | DDR3 SDRAM Bank Address Outputs |

| … | n/a | … | DDR3 other signals |

HC595

| Chip | Pin | Description |

|---|---|---|

| U22 | Qa | lan8 LED 0 (?) |

| U22 | Qb | lan8 LED 1 (?) |

| U22 | Qc | lan8 LED 2 (?) |

| U22 | Qd | lan7 LED 0 (?) |

| U22 | Qe | lan7 LED 1 (?) |

| U22 | Qf | lan7 LED 2 (?) |

| U22 | Qg | lan6 LED 0 (?) |

| U22 | Qh | lan6 LED 1 (?) |

| U21 | Qa | lan6 LED 2 (?) |

| U21 | Qb | lan5 LED 0 (?) |

| U21 | Qc | lan5 LED 1 (?) |

| U21 | Qd | lan5 LED 2 (?) |

| U21 | Qe | lan4 LED 0 (?) |

| U21 | Qf | lan4 LED 1 (?) |

| U21 | Qg | lan4 LED 2 (?) |

| U21 | Qh | lan3 LED 0 (?) |

| U20 | Qa | lan3 LED 1 (?) |

| U20 | Qb | lan3 LED 2 (?) |

| U20 | Qc | lan2 LED 0 (?) |

| U20 | Qd | lan2 LED 1 (?) |

| U20 | Qe | lan1 LED 2 (?) |

| U20 | Qf | lan1 LED 0 (?) |

| U20 | Qg | lan1 LED 1 (?) |

| U20 | Qh | lan1 LED 2 (?) |

PoE 8051

| Pin | Description |

|---|---|

| P3.0 | UART RxD |

| P3.1 | UART TxD |

| P3.2 | PoE SCK |

| P3.3 | PoE SDA |

| P3.4 | lan1 PoE LED (active low) |

| P3.5 | lan2 PoE LED (active low) |

| P3.6 | lan3 PoE LED (active low) |

| P3.7 | lan4 PoE LED (active low) |

| P1.0 | lan5 PoE LED (active low) |

| P1.1 | lan6 PoE LED (active low) |

| P1.6 | lan7 PoE LED (active low) |

| P1.7 | lan8 PoE LED (active low) |

| P5.5 | FAN PWM (FET not populated) |

Photos

Log Data

console boot

U-Boot 2011.12.(3.6.6.55087) (Dec 11 2021 - 18:17:40)

Board: RTL9300 CPU:800MHz LX:175MHz DDR:600MHz

DRAM: 256 MB

SPI-F: FUDANWEI/A14018/MMIO16-1/ModeC 1x16 MB (plr_flash_info @ 83f9ddf8)

Loading 65536B env. variables from offset 0xe0000

Net: Net Initialization Skipped

No ethernet found.

Hit Esc key to stop autoboot: 0

## Booting kernel from Legacy Image at b4300000 ...

Image Name: 1.0.0.0

Created: 2022-07-30 16:53:57 UTC

Image Type: MIPS Linux Kernel Image (lzma compressed)

Data Size: 8564103 Bytes = 8.2 MB

Load Address: 80000000

Entry Point: 8032ed60

Verifying Checksum ... OK

Uncompressing Kernel Image ... OK

Starting kernel ...

console [ttyS0] enabled

bootconsole [early0] disabled

Calibrating delay loop... 531.66 BogoMIPS (lpj=2658304)

pid_max: default: 32768 minimum: 301

Mount-cache hash table entries: 1024 (order: 0, 4096 bytes)

Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes)

NET: Registered protocol family 16

SCSI subsystem initialized

usbcore: registered new interface driver usbfs

usbcore: registered new interface driver hub

usbcore: registered new device driver usb

NET: Registered protocol family 2

TCP established hash table entries: 2048 (order: 1, 8192 bytes)

TCP bind hash table entries: 2048 (order: 3, 40960 bytes)

TCP: Hash tables configured (established 2048 bind 2048)

TCP: reno registered

UDP hash table entries: 256 (order: 1, 12288 bytes)

UDP-Lite hash table entries: 256 (order: 1, 12288 bytes)

NET: Registered protocol family 1

futex hash table entries: 256 (order: 0, 7168 bytes)

squashfs: version 4.0 (2009/01/31) Phillip Lougher

ntfs: driver 2.1.31 [Flags: R/W].

jffs2: version 2.2. (NAND) © 2001-2006 Red Hat, Inc.

msgmni has been set to 485

random: modprobe urandom read with 0 bits of entropy available

io scheduler noop registered

io scheduler deadline registered

io scheduler cfq registered (default)

Serial: 8250/16550 driver, 1 ports, IRQ sharing disabled

serial8250: ttyS0 at MMIO 0x0 (irq = 47, base_baud = 10879900) is a 16550A

loop: module loaded

SCSI Media Changer driver v0.25

RTK_SPI_FLASH_MIO driver is bypassed

RTK_NORSFG3 driver is used

=================================================================

init_luna_nor_spi_map: flash map at 0xb4000000

SPI NOR driver probe...

=====Fudanwei======/A14018/MMIO16-1/ModeC add SPI NOR partition

MTD partitions obtained from built-in array

Creating 7 MTD partitions on "rtk_norsf_g3":

0x000000000000-0x0000000e0000 : "LOADER"

0x0000000e0000-0x0000000f0000 : "BDINFO"

0x0000000f0000-0x000000100000 : "SYSINFO"

0x000000100000-0x000000200000 : "JFFS2 CFG"

0x000000200000-0x000000300000 : "JFFS2 LOG"

0x000000300000-0x000000f00000 : "RUNTIME"

0x000000f00000-0x000001000000 : "OEMINFO"

=================================================================

ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

rtk_gen1_hcd_cs_init: rtk_gen1_hcd_cs_init()!

rtk_gen1_hcd_cs_init: register rtk_gen1_ehci ok!

usb_phy_configure_process: usb_phy_configure_process()!

rtk_gen1-ehci rtk_gen1-ehci: Realtek On-Chip EHCI Host Controller

rtk_gen1-ehci rtk_gen1-ehci: new USB bus registered, assigned bus number 1

rtk_gen1-ehci rtk_gen1-ehci: irq 28, io mem 0x18021000

rtk_gen1-ehci rtk_gen1-ehci: USB 2.0 started, EHCI 1.00

hub 1-0:1.0: USB hub found

hub 1-0:1.0: 1 port detected

ohci_hcd: USB 1.1 'Open' Host Controller (OHCI) Driver

ohci-platform: OHCI generic platform driver

usbcore: registered new interface driver uas

usbcore: registered new interface driver usb-storage

TCP: cubic registered

NET: Registered protocol family 10

sit: IPv6 over IPv4 tunneling driver

NET: Registered protocol family 17

Freeing unused kernel memory: 6876K (80459000 - 80b10000)

Mount DEV File System....OK

Mount PROC File System........OK

Mount Main SQFS File System........OK

Mount Module SQFS File System....OK

Mount CFG JFFS2 File System....OK

Mount LOG JFFS2 File System....OK

Mount OEM JFFS2 File System....OK

RTCORE LKM Insert...

RTCORE Driver Module Initialize

IOAL init

Log init

Hardware-profile probe (RTL9303_8X8226)

Hardware-profile init

GPIO probe (unit 0): (found)

GPIO Init

SPI init (unit 0)

Intr Probe (unit 0)

TC probe (unit 0): (found)

TC init (unit 0)

TC util init (unit 0)

TC util init (isr)

Watchdog probe (unit 0): (found)

Watchdog init (unit 0)

I2C probe (unit 0)

RTL8231 probe (unit 0): (found)

RTL8231 init (unit 0)

UART probe (unit 0): (found)

NIC probe (unit 0)

IOAL init

L2Ntfy probe (unit 0): (found)

RTK Driver Module Initialize

MAC probe (unit 0)

Chip 9303 (found)

MAC init (unit 0)

@@@@@@@@@@@@@@@@@@@@@@@ret= 0,val= fff

SMI protocol probe (unit 0)

unit=0 port=0 smi=0 C45=1 C22=1

unit=0 port=8 smi=0 C45=1 C22=1

unit=0 port=16 smi=0 C45=1 C22=1

unit=0 port=20 smi=0 C45=1 C22=1

unit=0 port=24 smi=1 C45=1 C22=1

unit=0 port=25 smi=1 C45=1 C22=1

unit=0 port=26 smi=1 C45=1 C22=1

unit=0 port=27 smi=1 C45=1 C22=1

PHY probe (unit 0)

PHY driver probed on unit 0 port 0

PHY driver probed on unit 0 port 8

PHY driver probed on unit 0 port 16

PHY driver probed on unit 0 port 20

PHY driver probed on unit 0 port 24

PHY driver probed on unit 0 port 25

PHY driver probed on unit 0 port 26

PHY driver probed on unit 0 port 27

Chip Construct (unit 0)

Chip Construct

Disable PHY Polling

PHY Reset

MAC Construct

Turn Off Serdes

Serdes Construct

PHY Construct

Turn On Serdes

Mac_Polling_PHY Config

Enable PHY Polling

Misc

PHY init (unit 0)

Mgmt_dev init (unit 0)

RTDRV Driver Module Initialize

[GPIO] Initial External Device 1 mode 1 address 0

[GPIO] Initial Internal pin 0 direction OUT default 0

[GPIO] Initial Internal pin 1 direction OUT default 0

[GPIO] Initial External1 pin 0 direction IN default 0

[GPIO] Initial External1 pin 1 direction IN default 0

[GPIO] Initial External1 pin 3 direction IN default 0

[GPIO] Initial External1 pin 4 direction IN default 0

[GPIO] Initial External1 pin 5 direction IN default 0

[GPIO] Initial External1 pin 6 direction IN default 0

[GPIO] Initial External1 pin 7 direction IN default 0

[GPIO] Initial External1 pin 8 direction IN default 0

[GPIO] Initial External1 pin 9 direction IN default 0

[GPIO] Initial External1 pin 12 direction IN default 0

[GPIO] Initial External1 pin 13 direction IN default 0

[GPIO] Initial External1 pin 14 direction IN default 0

[GPIO] Initial External1 pin 21 direction IN default 0

[GPIO] Initial External1 pin 24 direction IN default 0

[GPIO] Initial External1 pin 25 direction IN default 0

[GPIO] Initial External1 pin 26 direction IN default 0

[GPIO] Initial External1 pin 33 direction IN default 0

==================Board ID: 9300022====================

==================Force Boardmodel With WEB Always.==================

==================Force Boardmodel With PoE==================.

==================Check the PSE existed or not.==================

==================Check the PSE existed or not result: Has PSE.==================

==================Try to Get the PSE Infromation.==================

==================Already Got the bt_port_no Infromation.==================

==================Already Got the pse_bank_pwr Infromation.==================

==================PSE Infromation.==================

==================PSE Infromation. PSE BT Port Number = 1==================

==================PSE Infromation. PSE Power Bank(walt) = 120==================

Init Board Configuration Module....OK

net: module license 'Realtek Semiconductor Corp.' taints kernel.

Disabling lock debugging due to kernel taint

Init Net Module....OK

Init Define Database Module....OK

Init KSI Core Driver Module....OK

Init OS Abstract Layer Module....OK

Init SKI Core Driver Module....OK

OK

Init Board Module....

Init Board Module-->watchdog....OK

Init Board Module-->led....OK

Init Board Module-->fiber....OK

Init Board Module-->POE....init the pse led controlled iic interface

init the pse led controlled iic interface

init the pse led controlled iic interface

init the pse led controlled iic interface

init the pse led controlled iic interface

init the pse led controlled iic interface

init the pse led controlled iic interface

init the pse led controlled iic interface

OK

Init Board Module-->BUTTON....

board_button_dumbmode_init

board_button_isolation_init

board_button_reset_init

OKOK

POEDOG ON

Init Board Vendor Module....OK

Init Switch STP Module....OK

Init Switch LACP Module....OK

Init Switch Multicast Module....OK

Init Custom Module....OK

Init OEM_INFOR ....OK

@@@@@@@@@@@@initd starts@@@@@@@@@@@@

====== Defaults Initial [Start] ======

Init Switch Factory Default....OK

Init VLAN Factory Default....OK

Init Mirror Factory Default....OK

Init L2 Factory Default....OK

Init Trunk Factory Default....OK

Init Rate Factory Default....OK

Init QoS Factory Default....OK

Init LACP Factory Default....OK

Init EEE Factory Default....OK

Init IGMP Factory Default....OK

Init STP Factory Default....OK

Init System Factory Default....OK

Init SNMP Factory Default....OK

Init Syslog Factory Default....OK

Init Custom Factory Default....OK

====== With PoE boardmodel Start.======

====== With PoE boardmodel End.======

Init POE Factory Default....OK

@@@@@@@@@@@@@@@@@@@in oem_config file: fds default ipaddr=192.168.2.1

@@@@@@@@@@@@@@@@@@@in uboot enviroment file: fds default ipaddr=192.168.0.1

Init Oem config Factory Default....OK

====== Defaults Initial [Done] ======

====== Initial from startup-config [Start] ======

====== Initial from startup-config [Done] ======

====== Post Initial [Start] ======

System Post Initial....OK

Port Post Initial....OK

====== Post Initial [Done] ======

*Jan 01 2022 00:00:03: %SYSTEM-5-COLDSTART: Cold@@@@@@@@@@@@initd ends@@@@@@@@@@@@

startup

@@@@@@@@@@@@timd starts@@@@@@@@@@@@

Press any key to continue

Username:

uboot version

RTL9300# # version U-Boot 2011.12.(3.6.6.55087) (Dec 11 2021 - 18:17:40) mips-linux-uclibc-xgcc (Realtek MSDK-4.8.5p1 Build 2536) 4.8.5 20150209 (prerelease) GNU ld (Realtek MSDK-4.8.5p1 Build 2536) 2.24.0

uboot printenv

RTL9300# # printenv baudrate=38400 boardmodel=RTL9303_8X8226 bootargs=bootm 0xb4300000 bootcmd=bootm 0xb4300000 bootdelay=1 ethact=rtl9300#0 ethaddr=00:28:24:12:92:97 fdsgwipaddr=192.168.0.254 fdsipaddr=192.168.0.1 fdsipmask=255.255.255.0 ipaddr=192.168.0.1 ledModeInitSkip=0 logoHref=http://www.hasivo.com/ logoName=hasivo logoYear=2022 modelname=S1100WP-8GT_SE pse_bt_port_no=1 pse_existed_flag=on pse_power_bank=120 serialnumber=sn02879583 serverip=192.168.0.111 stderr=serial stdin=serial stdout=serial sysName=Switch Environment size: 553/65532 bytes

uboot flshow

RTL9300# # printenv baudrate=38400 boardmodel=RTL9303_8X8226 bootargs=bootm 0xb4300000 bootcmd=bootm 0xb4300000 bootdelay=1 ethact=rtl9300#0 ethaddr=00:28:24:12:92:97 fdsgwipaddr=192.168.0.254 fdsipaddr=192.168.0.1 fdsipmask=255.255.255.0 ipaddr=192.168.0.1 ledModeInitSkip=0 logoHref=http://www.hasivo.com/ logoName=hasivo logoYear=2022 modelname=S1100WP-8GT_SE pse_bt_port_no=1 pse_existed_flag=on pse_power_bank=120 serialnumber=sn02879583 serverip=192.168.0.111 stderr=serial stdin=serial stdout=serial sysName=Switch Environment size: 553/65532 bytes

uboot flshow

RTL9300# # flshow =============== FLASH Partition Layout =============== Index Name Size Address ------------------------------------------------------ 0 LOADER 0xe0000 0xb4000000-0xb40dffff 1 BDINFO 0x10000 0xb40e0000-0xb40effff 2 SYSINFO 0x10000 0xb40f0000-0xb40fffff 3 JFFS2_CFG 0x100000 0xb4100000-0xb41fffff 4 JFFS2_LOG 0x100000 0xb4200000-0xb42fffff 5 RUNTIME1 0xc00000 0xb4300000-0xb4efffff 6 OEMINFO 0x100000 0xb4f00000-0xb4ffffff ======================================================

uboot show hw_profile_list

RTL9300# # rtk show hw_profile_list

Available profiles are:

RTL9301_2x8214QF_4XGE (9300001)

RTL9301_3x8218B_4XGE (9300002)

RTL9301_8218B_4XGE (9300003)

RTL9301_8218B_4XGE_CASCADE (9300004)

RTL9301_2x8214QF_4XGE_CASCADE (9300005)

RTL9301_14QF_4XGE_18B_4XGE_CASCADE (9300006)

RTL9301_3x8218D_4XGE (9300007)

RTL9301_1x8218D_4XGE (9300008)

RTL9301_2x8218D_4XGE (9300009)

RTL9301_6x8214QF_4XGE (9300010)

RTL9301_2x8214FC_4x8214QF_4XGE (9300011)

RTL9301_6x8218D_2x8295R_CASCADE (9300012)

RTL9301_2x8218B_4x8218D_2x8295R_CASCADE (9300013)

RTL9302B_2x8218D_2xCUST1_4xGE (9300014)

RTL9302C_4xCUST1 (9300015)

RTL9303_2xCUST1 (9300016)

RTL9303_8XGE (9300017)

RTL9303_8X2_5G (9300027)

RTL9303_8X8226 (9300022)

RTL9302DE_2XRTL8284 (9300018)

RTL9302C_2xRTL8284_2XGE (9300019)

RTL9302C_4xRTL8284_4XGE (9300020)

RTL9302B_2x8218D_2x8284_4xGE (9300021)

RTL9301_3x8218D_2x8226CARD_2XGE (9300023)

RTL9301_2x8214FC_4x8214QF_4XGE_KD (9300024)

RTL9301_2x8214FC_4x8214QF_4XGE_HAISI (9300026)

RTL9301_3x8218D_4XGE_HR (9300025)

RTL9301_3x8218E_4XGE (9300028)

RTL9303_2X8254L_DEMO (9300029)

RTL9303_6x8254L_6xSPI (9300030)

(uboot: setenv boardmodel 'YOUR_HARDWARE_PROFILE_NAME')

uboot show tech-support

Switch# show tech-support

!!!!

------------------ System Information ------------------

Model : S1100WP-8GT_SE

System Name : Switch

System Location : default

System Contact : default

MAC Address : 00:28:24:12:92:97

IP Address : 192.168.0.1

Subnet Mask : 255.255.255.0

Loader Version : 3.6.6.55087

Loader Date : Dec 11 2021 - 18:17:40

Firmware Version : 1.0.0.0

Firmware Date : Jul 30 2022 - 16:53:57

System Up Time : 0 days, 0 hours, 0 mins, 44 secs

------------------ Time ------------------

2022-01-01 08:00:44 UTC+8

Time set manually

Time zone:

Acronym is

Offset is UTC+8

------------------ User Status ------------------

Username Protocol Location

--------------- ------------ -----------------------

admin console 0.0.0.0

------------------ Startup-config ------------------

SYSTEM CONFIG FILE ::= BEGIN

! System Description: KT-NOS S1100WP-8GT_SE Switch

! System Version: v1.0.0.0

! System Name: Switch

! System Up Time: 0 days, 0 hours, 1 mins, 44 secs

!

!

!

system location "default"

system contact "default"

no ip dhcp

ip address 192.168.0.1 mask 255.255.255.0

username "admin" secret encrypted MjEyMzJmMjk3YTU3YTVhNzQzODk0YTBlNGE4MDFmYzM=

enable secret "ZDQxZDhjZDk4ZjAwYjIwNGU5ODAwOTk4ZWNmODQyN2U="

!

!

!

!

spanning-tree mst configuration

name "00:28:24:12:92:97"

!

snmp community "private" rw

snmp host 1.1.1.254 version 2c "private"

snmp

ip telnet

ip ssh

ip https

!

!

!

interface mgi1

poe type bt

!

interface mgi2

poe type at

!

interface mgi3

poe type at

!

interface mgi4

poe type at

!

interface mgi5

poe type at

!

interface mgi6

poe type at

!

interface mgi7

poe type at

!

interface mgi8

poe type at

!

!

!

!

!

------------------ Running-config ------------------

SYSTEM CONFIG FILE ::= BEGIN

! System Description: KT-NOS S1100WP-8GT_SE Switch

! System Version: v1.0.0.0

! System Name: Switch

! System Up Time: 0 days, 0 hours, 0 mins, 44 secs

!

!

!

system location "default"

system contact "default"

no ip dhcp

ip address 192.168.0.1 mask 255.255.255.0

username "admin" secret encrypted MjEyMzJmMjk3YTU3YTVhNzQzODk0YTBlNGE4MDFmYzM=

enable secret "ZDQxZDhjZDk4ZjAwYjIwNGU5ODAwOTk4ZWNmODQyN2U="

!

!

!

!

spanning-tree mst configuration

name "00:28:24:12:92:97"

!

snmp community "private" rw

snmp host 1.1.1.254 version 2c "private"

snmp

ip telnet

ip ssh

ip https

!

!

!

interface mgi1

poe type bt

!

interface mgi2

poe type at

!

interface mgi3

poe type at

!

interface mgi4

poe type at

!

interface mgi5

poe type at

!

interface mgi6

poe type at

!

interface mgi7

poe type at

!

interface mgi8

poe type at

!

!

!

!

!

------------------ Board Configuration ------------------

****************************

RTL9301-8X2P5GE

****************************

============================

Board GPIO

============================

Device Pin Direction Default Current Purpose

------- ---- ---------- -------- -------- --------

INT 0 OUT 0 1

INT 1 OUT 0 0

INT 8 IN 0 1

INT 9 IN 0 1

INT 10 OUT 0 1

INT 11 IN 0 1

INT 12 IN 0 1

INT 14 OUT 0 1

INT 19 IN 0 0

INT 20 IN 0 0

INT 21 IN 0 1

INT 22 IN 0 1

INT 23 IN 0 1

EXT 0 IN (IN ) 0 0

EXT 1 IN (IN ) 0 0

EXT 3 IN (IN ) 0 0

EXT 4 IN (IN ) 0 0

EXT 5 IN (IN ) 0 0

EXT 6 IN (IN ) 0 0

EXT 7 IN (IN ) 0 0

EXT 8 IN (IN ) 0 0

EXT 9 IN (IN ) 0 0

EXT 12 IN (IN ) 0 0

EXT 13 IN (IN ) 0 0

EXT 14 IN (IN ) 0 0

EXT 21 IN (IN ) 0 0

EXT 24 IN (IN ) 0 0

EXT 25 IN (IN ) 0 0

EXT 26 IN (IN ) 0 0

EXT 33 IN (IN ) 0 0

============================

Board Configuration

============================

====== Port ==================

Type Usr Phy Media Speed Duplex Attr

----------- ---- ------- ----------- -------------- -------- -------

10G 1 (0) 0 Copper Auto 1

10G 2 (0) 8 Copper Auto 1

10G 3 (0) 16 Copper Auto 1

10G 4 (0) 20 Copper Auto 1

10G 5 (0) 24 Copper Auto 1

10G 6 (0) 25 Copper Auto 1

10G 7 (0) 26 Copper Auto 1

10G 8 (0) 27 Copper Auto 1

====== Led ===================

SYS (GPIO Blink)

ALARM (REG)

====== WatchDog ==============

Type: REG

------------------ IP Configuration ------------------

------------------ Spanning-Tree ------------------

msti 0 port 0 state Frw (Frw)

msti 0 port 1 state Dsbl (Dsbl)

msti 0 port 2 state Dsbl (Dsbl)

msti 0 port 3 state Dsbl (Dsbl)

msti 0 port 4 state Dsbl (Dsbl)

msti 0 port 5 state Dsbl (Dsbl)

msti 0 port 6 state Dsbl (Dsbl)

msti 0 port 7 state Dsbl (Dsbl)

msti 0 port 8 state Dsbl (Dsbl)

msti 0 port 9 state Dsbl (Dsbl)

msti 0 port 10 state Dsbl (Dsbl)

msti 0 port 11 state Dsbl (Dsbl)

msti 0 port 12 state Dsbl (Dsbl)

msti 0 port 13 state Dsbl (Dsbl)

msti 0 port 14 state Dsbl (Dsbl)

msti 0 port 15 state Dsbl (Dsbl)

msti 1 port 0 state Frw (Frw)

msti 1 port 1 state Dsbl (Dsbl)

msti 1 port 2 state Dsbl (Dsbl)

msti 1 port 3 state Dsbl (Dsbl)

msti 1 port 4 state Dsbl (Dsbl)

msti 1 port 5 state Dsbl (Dsbl)

msti 1 port 6 state Dsbl (Dsbl)

msti 1 port 7 state Dsbl (Dsbl)

msti 1 port 8 state Dsbl (Dsbl)

msti 1 port 9 state Dsbl (Dsbl)

msti 1 port 10 state Dsbl (Dsbl)

msti 1 port 11 state Dsbl (Dsbl)

msti 1 port 12 state Dsbl (Dsbl)

msti 1 port 13 state Dsbl (Dsbl)

msti 1 port 14 state Dsbl (Dsbl)

msti 1 port 15 state Dsbl (Dsbl)

msti 2 port 0 state Frw (Frw)

msti 2 port 1 state Dsbl (Dsbl)

msti 2 port 2 state Dsbl (Dsbl)

msti 2 port 3 state Dsbl (Dsbl)

msti 2 port 4 state Dsbl (Dsbl)

msti 2 port 5 state Dsbl (Dsbl)

msti 2 port 6 state Dsbl (Dsbl)

msti 2 port 7 state Dsbl (Dsbl)

msti 2 port 8 state Dsbl (Dsbl)

msti 2 port 9 state Dsbl (Dsbl)

msti 2 port 10 state Dsbl (Dsbl)

msti 2 port 11 state Dsbl (Dsbl)

msti 2 port 12 state Dsbl (Dsbl)

msti 2 port 13 state Dsbl (Dsbl)

msti 2 port 14 state Dsbl (Dsbl)

msti 2 port 15 state Dsbl (Dsbl)

msti 3 port 0 state Frw (Frw)

msti 3 port 1 state Dsbl (Dsbl)

msti 3 port 2 state Dsbl (Dsbl)

msti 3 port 3 state Dsbl (Dsbl)

msti 3 port 4 state Dsbl (Dsbl)

msti 3 port 5 state Dsbl (Dsbl)

msti 3 port 6 state Dsbl (Dsbl)

msti 3 port 7 state Dsbl (Dsbl)

msti 3 port 8 state Dsbl (Dsbl)

msti 3 port 9 state Dsbl (Dsbl)

msti 3 port 10 state Dsbl (Dsbl)

msti 3 port 11 state Dsbl (Dsbl)

msti 3 port 12 state Dsbl (Dsbl)

msti 3 port 13 state Dsbl (Dsbl)

msti 3 port 14 state Dsbl (Dsbl)

msti 3 port 15 state Dsbl (Dsbl)

msti 4 port 0 state Frw (Frw)

msti 4 port 1 state Dsbl (Dsbl)

msti 4 port 2 state Dsbl (Dsbl)

msti 4 port 3 state Dsbl (Dsbl)

msti 4 port 4 state Dsbl (Dsbl)

msti 4 port 5 state Dsbl (Dsbl)

msti 4 port 6 state Dsbl (Dsbl)

msti 4 port 7 state Dsbl (Dsbl)

msti 4 port 8 state Dsbl (Dsbl)

msti 4 port 9 state Dsbl (Dsbl)

msti 4 port 10 state Dsbl (Dsbl)

msti 4 port 11 state Dsbl (Dsbl)

msti 4 port 12 state Dsbl (Dsbl)

msti 4 port 13 state Dsbl (Dsbl)

msti 4 port 14 state Dsbl (Dsbl)

msti 4 port 15 state Dsbl (Dsbl)

msti 5 port 0 state Frw (Frw)

msti 5 port 1 state Dsbl (Dsbl)

msti 5 port 2 state Dsbl (Dsbl)

msti 5 port 3 state Dsbl (Dsbl)

msti 5 port 4 state Dsbl (Dsbl)

msti 5 port 5 state Dsbl (Dsbl)

msti 5 port 6 state Dsbl (Dsbl)

msti 5 port 7 state Dsbl (Dsbl)

msti 5 port 8 state Dsbl (Dsbl)

msti 5 port 9 state Dsbl (Dsbl)

msti 5 port 10 state Dsbl (Dsbl)

msti 5 port 11 state Dsbl (Dsbl)

msti 5 port 12 state Dsbl (Dsbl)

msti 5 port 13 state Dsbl (Dsbl)

msti 5 port 14 state Dsbl (Dsbl)

msti 5 port 15 state Dsbl (Dsbl)

msti 6 port 0 state Frw (Frw)

msti 6 port 1 state Dsbl (Dsbl)

msti 6 port 2 state Dsbl (Dsbl)

msti 6 port 3 state Dsbl (Dsbl)

msti 6 port 4 state Dsbl (Dsbl)

msti 6 port 5 state Dsbl (Dsbl)

msti 6 port 6 state Dsbl (Dsbl)

msti 6 port 7 state Dsbl (Dsbl)

msti 6 port 8 state Dsbl (Dsbl)

msti 6 port 9 state Dsbl (Dsbl)

msti 6 port 10 state Dsbl (Dsbl)

msti 6 port 11 state Dsbl (Dsbl)

msti 6 port 12 state Dsbl (Dsbl)

msti 6 port 13 state Dsbl (Dsbl)

msti 6 port 14 state Dsbl (Dsbl)

msti 6 port 15 state Dsbl (Dsbl)

msti 7 port 0 state Frw (Frw)

msti 7 port 1 state Dsbl (Dsbl)

msti 7 port 2 state Dsbl (Dsbl)

msti 7 port 3 state Dsbl (Dsbl)

msti 7 port 4 state Dsbl (Dsbl)

msti 7 port 5 state Dsbl (Dsbl)

msti 7 port 6 state Dsbl (Dsbl)

msti 7 port 7 state Dsbl (Dsbl)

msti 7 port 8 state Dsbl (Dsbl)

msti 7 port 9 state Dsbl (Dsbl)

msti 7 port 10 state Dsbl (Dsbl)

msti 7 port 11 state Dsbl (Dsbl)

msti 7 port 12 state Dsbl (Dsbl)

msti 7 port 13 state Dsbl (Dsbl)

msti 7 port 14 state Dsbl (Dsbl)

msti 7 port 15 state Dsbl (Dsbl)

msti 8 port 0 state Frw (Frw)

msti 8 port 1 state Dsbl (Dsbl)

msti 8 port 2 state Dsbl (Dsbl)

msti 8 port 3 state Dsbl (Dsbl)

msti 8 port 4 state Dsbl (Dsbl)

msti 8 port 5 state Dsbl (Dsbl)

msti 8 port 6 state Dsbl (Dsbl)

msti 8 port 7 state Dsbl (Dsbl)

msti 8 port 8 state Dsbl (Dsbl)

msti 8 port 9 state Dsbl (Dsbl)

msti 8 port 10 state Dsbl (Dsbl)

msti 8 port 11 state Dsbl (Dsbl)

msti 8 port 12 state Dsbl (Dsbl)

msti 8 port 13 state Dsbl (Dsbl)

msti 8 port 14 state Dsbl (Dsbl)

msti 8 port 15 state Dsbl (Dsbl)

msti 9 port 0 state Frw (Frw)

msti 9 port 1 state Dsbl (Dsbl)

msti 9 port 2 state Dsbl (Dsbl)

msti 9 port 3 state Dsbl (Dsbl)

msti 9 port 4 state Dsbl (Dsbl)

msti 9 port 5 state Dsbl (Dsbl)

msti 9 port 6 state Dsbl (Dsbl)

msti 9 port 7 state Dsbl (Dsbl)

msti 9 port 8 state Dsbl (Dsbl)

msti 9 port 9 state Dsbl (Dsbl)

msti 9 port 10 state Dsbl (Dsbl)

msti 9 port 11 state Dsbl (Dsbl)

msti 9 port 12 state Dsbl (Dsbl)

msti 9 port 13 state Dsbl (Dsbl)

msti 9 port 14 state Dsbl (Dsbl)

msti 9 port 15 state Dsbl (Dsbl)

msti 10 port 0 state Frw (Frw)

msti 10 port 1 state Dsbl (Dsbl)

msti 10 port 2 state Dsbl (Dsbl)

msti 10 port 3 state Dsbl (Dsbl)

msti 10 port 4 state Dsbl (Dsbl)

msti 10 port 5 state Dsbl (Dsbl)

msti 10 port 6 state Dsbl (Dsbl)

msti 10 port 7 state Dsbl (Dsbl)

msti 10 port 8 state Dsbl (Dsbl)

msti 10 port 9 state Dsbl (Dsbl)

msti 10 port 10 state Dsbl (Dsbl)

msti 10 port 11 state Dsbl (Dsbl)

msti 10 port 12 state Dsbl (Dsbl)

msti 10 port 13 state Dsbl (Dsbl)

msti 10 port 14 state Dsbl (Dsbl)

msti 10 port 15 state Dsbl (Dsbl)

msti 11 port 0 state Frw (Frw)

msti 11 port 1 state Dsbl (Dsbl)

msti 11 port 2 state Dsbl (Dsbl)

msti 11 port 3 state Dsbl (Dsbl)

msti 11 port 4 state Dsbl (Dsbl)

msti 11 port 5 state Dsbl (Dsbl)

msti 11 port 6 state Dsbl (Dsbl)

msti 11 port 7 state Dsbl (Dsbl)

msti 11 port 8 state Dsbl (Dsbl)

msti 11 port 9 state Dsbl (Dsbl)

msti 11 port 10 state Dsbl (Dsbl)

msti 11 port 11 state Dsbl (Dsbl)

msti 11 port 12 state Dsbl (Dsbl)

msti 11 port 13 state Dsbl (Dsbl)

msti 11 port 14 state Dsbl (Dsbl)

msti 11 port 15 state Dsbl (Dsbl)

msti 12 port 0 state Frw (Frw)

msti 12 port 1 state Dsbl (Dsbl)

msti 12 port 2 state Dsbl (Dsbl)

msti 12 port 3 state Dsbl (Dsbl)

msti 12 port 4 state Dsbl (Dsbl)

msti 12 port 5 state Dsbl (Dsbl)

msti 12 port 6 state Dsbl (Dsbl)

msti 12 port 7 state Dsbl (Dsbl)

msti 12 port 8 state Dsbl (Dsbl)

msti 12 port 9 state Dsbl (Dsbl)

msti 12 port 10 state Dsbl (Dsbl)

msti 12 port 11 state Dsbl (Dsbl)

msti 12 port 12 state Dsbl (Dsbl)

msti 12 port 13 state Dsbl (Dsbl)

msti 12 port 14 state Dsbl (Dsbl)

msti 12 port 15 state Dsbl (Dsbl)

msti 13 port 0 state Frw (Frw)

msti 13 port 1 state Dsbl (Dsbl)

msti 13 port 2 state Dsbl (Dsbl)

msti 13 port 3 state Dsbl (Dsbl)

msti 13 port 4 state Dsbl (Dsbl)

msti 13 port 5 state Dsbl (Dsbl)

msti 13 port 6 state Dsbl (Dsbl)

msti 13 port 7 state Dsbl (Dsbl)

msti 13 port 8 state Dsbl (Dsbl)

msti 13 port 9 state Dsbl (Dsbl)

msti 13 port 10 state Dsbl (Dsbl)

msti 13 port 11 state Dsbl (Dsbl)

msti 13 port 12 state Dsbl (Dsbl)

msti 13 port 13 state Dsbl (Dsbl)

msti 13 port 14 state Dsbl (Dsbl)

msti 13 port 15 state Dsbl (Dsbl)

msti 14 port 0 state Frw (Frw)

msti 14 port 1 state Dsbl (Dsbl)

msti 14 port 2 state Dsbl (Dsbl)

msti 14 port 3 state Dsbl (Dsbl)

msti 14 port 4 state Dsbl (Dsbl)

msti 14 port 5 state Dsbl (Dsbl)

msti 14 port 6 state Dsbl (Dsbl)

msti 14 port 7 state Dsbl (Dsbl)

msti 14 port 8 state Dsbl (Dsbl)

msti 14 port 9 state Dsbl (Dsbl)

msti 14 port 10 state Dsbl (Dsbl)

msti 14 port 11 state Dsbl (Dsbl)

msti 14 port 12 state Dsbl (Dsbl)

msti 14 port 13 state Dsbl (Dsbl)

msti 14 port 14 state Dsbl (Dsbl)

msti 14 port 15 state Dsbl (Dsbl)

msti 15 port 0 state Frw (Frw)

msti 15 port 1 state Dsbl (Dsbl)

msti 15 port 2 state Dsbl (Dsbl)

msti 15 port 3 state Dsbl (Dsbl)

msti 15 port 4 state Dsbl (Dsbl)

msti 15 port 5 state Dsbl (Dsbl)

msti 15 port 6 state Dsbl (Dsbl)

msti 15 port 7 state Dsbl (Dsbl)

msti 15 port 8 state Dsbl (Dsbl)

msti 15 port 9 state Dsbl (Dsbl)

msti 15 port 10 state Dsbl (Dsbl)

msti 15 port 11 state Dsbl (Dsbl)

msti 15 port 12 state Dsbl (Dsbl)

msti 15 port 13 state Dsbl (Dsbl)

msti 15 port 14 state Dsbl (Dsbl)

msti 15 port 15 state Dsbl (Dsbl)

###### MST 0 Vlans Mapped: 1-4094

CST Root ID Priority 0

Address 00:00:00:00:00:00

Hello Time 2 sec Max Age 20 sec Forward Delay 15 sec

Max hops 20

Name State Prio.Nbr Cost Sts Role EdgePort Type

--------- -------- -------- -------- ------ ---- -------- -----------------

mgi1 disabled 128.1 20000 Frw Dsbl No P2P (RSTP)

------------------ Logging ------------------

Logging service is enabled

Aggregation: enabled

Aggregation aging time: 300 sec

Console Logging: level notice

Buffer Logging : level notice

File Logging : disabled

------------------ IGMP Snooping ------------------

IGMP Snooping Status

--------------------

Snooping : disabled

Report Suppression : disabled

Operation Version : v2

Forward Method : mac

Unknown IP Multicast Action : Flood

Packet Statistics

Total RX : 0

Valid RX : 0

Invalid RX : 0

Other RX : 0

Leave RX : 0

Report RX : 0

General Query RX : 0

Specail Group Query RX : 0

Specail Group & Source Query RX : 0

Leave TX : 0

Report TX : 0

General Query TX : 0

Specail Group Query TX : 0

Specail Group & Source Query TX : 0

VLAN | Group IP Address | Type | Life(Sec) | Port

------+------------------+--------+-----------+------------------

Total Number of Entry = 0

------------------ Interfaces ------------------

MultiGigabitEthernet1 is up

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

138 packets input, 27185 bytes, 0 throttles

Received 26 broadcasts (112 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

112 multicast, 0 pause input

0 input packets with dribble condition detected

1 packets output, 74 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

MultiGigabitEthernet2 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

MultiGigabitEthernet3 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

MultiGigabitEthernet4 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

MultiGigabitEthernet5 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

MultiGigabitEthernet6 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

MultiGigabitEthernet7 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

MultiGigabitEthernet8 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

LAG1 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

LAG2 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

LAG3 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

LAG4 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

LAG5 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

LAG6 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

LAG7 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

LAG8 is down

Hardware is Fast Ethernet

Auto-duplex, Auto-speed, media type is Copper

flow-control is off

back-pressure is enabled

0 packets input, 0 bytes, 0 throttles

Received 0 broadcasts (0 multicasts)

0 runts, 0 giants, 0 throttles

0 input errors, 0 CRC, 0 frame

0 multicast, 0 pause input

0 input packets with dribble condition detected

0 packets output, 0 bytes, 0 underrun

0 output errors, 0 collisions

0 babbles, 0 late collision, 0 deferred

0 PAUSE output

------------------ Interfaces Status ------------------

Port Status Duplex Speed Type

mgi1 connected a-full a-1000M Copper

mgi2 notconnect auto auto Copper

mgi3 notconnect auto auto Copper

mgi4 notconnect auto auto Copper

mgi5 notconnect auto auto Copper

mgi6 notconnect auto auto Copper

mgi7 notconnect auto auto Copper

mgi8 notconnect auto auto Copper

lag1 notconnect auto auto Copper

lag2 notconnect auto auto Copper

lag3 notconnect auto auto Copper

lag4 notconnect auto auto Copper

lag5 notconnect auto auto Copper

lag6 notconnect auto auto Copper

lag7 notconnect auto auto Copper

lag8 notconnect auto auto Copper

------------------ MAC Address Table ------------------

VID | MAC Address | Type | Ports

------+-------------------+-------------------+----------------

1 | 00:28:24:12:92:97 | Management | CPU

1 | D8:BB:C1:F5:6D:CB | Dynamic | mgi1

Total number of entries: 2

------------------ MAC Address Counters ------------------

Port Dynamic

----- --------------

mgi1 1

mgi2 0

mgi3 0

mgi4 0

mgi5 0

mgi6 0

mgi7 0

mgi8 0

lag1 0

lag2 0

lag3 0

lag4 0

lag5 0

lag6 0

lag7 0

lag8 0

----------------

Maximum: 16384

CPU: 1

Dynamic: 1

Static: 0

Multicast: 0

Blacklist: 0

----------------

Usage: 2

Available: 16382

------------------ ACL ------------------

Block 0:

Template idx 0: 0

Template idx 1: 5

Block 1:

Template idx 0: 0

Template idx 1: 0

Block 2:

Template idx 0: 0

Template idx 1: 0

Block 3:

Template idx 0: 0

Template idx 1: 0

Block 4:

Template idx 0: 0

Template idx 1: 0

Block 5:

Template idx 0: 0

Template idx 1: 0

Block 6:

Template idx 0: 0

Template idx 1: 0

Block 7:

Template idx 0: 0

Template idx 1: 0

Block 8:

Template idx 0: 0

Template idx 1: 0

Block 9:

Template idx 0: 0

Template idx 1: 0

Block 10:

Template idx 0: 0

Template idx 1: 0

Block 11:

Template idx 0: 0

Template idx 1: 0

Block 12:

Template idx 0: 0

Template idx 1: 0

Block 13:

Template idx 0: 0

Template idx 1: 0

Block 14:

Template idx 0: 0

Template idx 1: 0

Block 15:

Template idx 0: 0

Template idx 1: 0

Template 0 field info:

field 0: dmac0

field 1: dmac1

field 2: dmac2

field 3: smac0

field 4: smac1

field 5: smac2

field 6: vlan

field 7: ip-tos-proto

field 8: dsap-ssap

field 9: ethertype

field 10: spm0

field 11: spm1

Template 1 field info:

field 0: sip0

field 1: sip1

field 2: dip0

field 3: dip1

field 4: ip-tos-proto

field 5: tcp-info

field 6: l4-sport

field 7: l4-dport

field 8: vlan

field 9: range-check

field 10: spm0

field 11: spm1

Template 2 field info:

field 0: dmac0

field 1: dmac1

field 2: dmac2

field 3: vlan

field 4: ethertype

field 5: ip-tos-proto

field 6: sip0

field 7: sip1

field 8: dip0

field 9: dip1

field 10: l4-sport

field 11: l4-dport

Template 3 field info:

field 0: dip0

field 1: dip1

field 2: dip2

field 3: dip3

field 4: dip4

field 5: dip5

field 6: dip6

field 7: dip7

field 8: ip-tos-proto

field 9: tcp-info

field 10: l4-sport

field 11: l4-dport

Template 4 field info:

field 0: sip0

field 1: sip1

field 2: sip2

field 3: sip3

field 4: sip4

field 5: sip5

field 6: sip6

field 7: sip7

field 8: vlan

field 9: range-check

field 10: spm0

field 11: spm1

Template 5 field info:

field 0: dip0

field 1: dip1

field 2: ip-tos-proto

field 3: l4-dport

field 4: l4-sport

field 5: tcp-info

field 6: none

field 7: dip7

field 8: pkt-info

field 9: slp

field 10: spm0

field 11: spm1

Template 6 field info:

field 0: smac0

field 1: smac1

field 2: smac2

field 3: otag

field 4: sip0

field 5: sip1

field 6: ip-tos-proto

field 7: l4-dport

field 8: pkt-info

field 9: none

field 10: spm0

field 11: spm1

Template 7 field info:

field 0: none

field 1: none

field 2: none

field 3: none

field 4: none

field 5: none

field 6: none

field 7: none

field 8: none

field 9: none

field 10: none

field 11: none

Template 8 field info:

field 0: none

field 1: none

field 2: none

field 3: none

field 4: none

field 5: none

field 6: none

field 7: none

field 8: none

field 9: none

field 10: none

field 11: none

Template 9 field info:

field 0: none

field 1: none

field 2: none

field 3: none

field 4: none

field 5: none

field 6: none

field 7: none

field 8: none

field 9: none

field 10: none

field 11: none

Block: 0 in phase 2 Ingrss ACL

Idx:0 (0)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|01:ff

19|80:ff

20|c2:ff

21|00:ff

22|00:ff

23|30:f0

24|00:00

25|00:00

26|00:01

Idx:1 (1)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:2 (2)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|01:ff

19|80:ff

20|c2:ff

21|00:ff

22|00:ff

23|40:c0

24|00:00

25|00:00

26|00:01

Idx:3 (3)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:4 (4)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|01:ff

19|80:ff

20|c2:ff

21|00:ff

22|00:ff

23|80:80

24|00:00

25|00:00

26|00:01

Idx:5 (5)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:6 (6)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|33:ff

19|33:ff

20|00:ff

21|01:ff

22|00:ff

23|02:ff

24|00:00

25|00:00

26|00:01

Idx:7 (7)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:8 (8)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|33:ff

19|33:ff

20|00:ff

21|00:ff

22|00:ff

23|16:ff

24|00:00

25|00:00

26|00:01

Idx:9 (9)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:10 (10)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|01:ff

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|42:42

26|00:01

Idx:11 (11)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:12 (12)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|06:ff

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|c2:c2

26|00:01

Idx:13 (13)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:ff

17|50:ff

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:14 (14)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|06:ff

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|c2:c2

26|00:01

Idx:15 (15)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|01:ff

17|bb:ff

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:16 (16)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|06:ff

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|c2:c2

26|00:01

Idx:17 (17)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:ff

17|16:ff

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:18 (18)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|06:ff

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|c2:c2

26|00:01

Idx:19 (19)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:ff

17|17:ff

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:20 (20)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|11:ff

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|c2:c2

26|00:01

Idx:21 (21)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:ff

17|a1:ff

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:22 (22)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|11:ff

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|c2:c2

26|00:01

Idx:23 (23)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:ff

17|45:ff

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:24 (24)

0|00:10

1|00:00

2|00:00

3|00:00

4|08:ff

5|06:ff

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:ff

13|28:ff

14|24:ff

15|12:ff

16|92:ff

17|97:ff

18|ff:ff

19|ff:ff

20|ff:ff

21|ff:ff

22|ff:ff

23|ff:ff

24|00:00

25|80:80

26|00:01

Idx:25 (25)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:26 (26)

0|00:10

1|00:00

2|00:00

3|00:00

4|08:ff

5|06:ff

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|40:40

26|00:01

Idx:27 (27)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:28 (28)

0|00:10

1|00:00

2|00:00

3|00:00

4|08:ff

5|06:ff

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|ff:ff

19|ff:ff

20|ff:ff

21|ff:ff

22|ff:ff

23|ff:ff

24|00:00

25|00:00

26|00:01

Idx:29 (29)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:30 (30)

0|00:10

1|00:00

2|00:00

3|00:00

4|86:ff

5|dd:ff

6|00:00

7|00:00

8|00:00

9|3a:ff

10|00:00

11|00:00

12|00:ff

13|28:ff

14|24:ff

15|12:ff

16|92:ff

17|97:ff

18|33:ff

19|33:ff

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|82:82

26|00:01

Idx:31 (31)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:32 (32)

0|00:10

1|00:00

2|00:00

3|00:00

4|86:ff

5|dd:ff

6|00:00

7|00:00

8|00:00

9|3a:ff

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|33:ff

19|33:ff

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|82:82

26|00:01

Idx:33 (33)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:34 (34)

0|00:00

1|00:00

2|00:00

3|00:00

4|86:ff

5|dd:ff

6|00:00

7|00:00

8|00:00

9|3a:ff

10|00:00

11|00:00

12|00:ff

13|28:ff

14|24:ff

15|12:ff

16|92:ff

17|97:ff

18|33:ff

19|33:ff

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|82:82

26|00:01

Idx:35 (35)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:36 (36)

0|00:10

1|00:00

2|00:00

3|00:00

4|86:ff

5|dd:ff

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|03:03

26|00:01

Idx:37 (37)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|ff:ff

9|00:f0

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

Idx:50 (50)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|01:ff

19|00:ff

20|5e:ff

21|00:ff

22|00:ff

23|00:00

24|00:00

25|02:03

26|00:01

Idx:51 (51)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|e0:ff

21|00:ff

22|00:ff

23|00:00

24|00:00

25|00:00

26|01:01

Idx:54 (54)

0|00:10

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|c0:c0

26|00:01

Idx:55 (55)

0|00:00

1|00:00

2|00:00

3|00:00

4|00:00

5|00:00

6|00:00

7|00:00

8|00:00

9|00:00

10|00:00

11|00:00

12|00:00

13|00:00

14|00:00

15|00:00

16|00:00

17|00:00

18|00:00

19|00:00

20|00:00

21|00:00

22|00:00

23|00:00

24|00:00

25|00:00

26|01:01

blk 1 type:NOT USE

blk 2 type:NOT USE

blk 3 type:NOT USE

blk 4 type:NOT USE

blk 5 type:NOT USE

blk 6 type:NOT USE

blk 7 type:NOT USE

blk 8 type:NOT USE

blk 9 type:NOT USE

blk 10 type:NOT USE

blk 11 type:NOT USE

blk 12 type:NOT USE

blk 13 type:NOT USE

blk 14 type:NOT USE

blk 15 type:NOT USE

------------------ VLAN ------------------

Management VLAN-ID : default(1)

Default VLAN-ID : 1

VID | VLAN Name | Untagged Ports | Tagged Ports | Type

-------+------------------+------------------------------+------------------------------+---------

1 | default | mgi1-8,lag1-8 | --- | Default

Port : mgi1

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : mgi2

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : mgi3

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : mgi4

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : mgi5

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : mgi6

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : mgi7

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : mgi8

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : lag1

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : lag2

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : lag3

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : lag4

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : lag5

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : lag6

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : lag7

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

Port : lag8

Port Mode : Trunk

Ingress Filtering : enabled

Acceptable Frame Type : all

Ingress UnTagged VLAN ( NATIVE ) : 1

Trunking VLANs Enabled:

Forbidden VLANs:

Vlan Name

------- -----------------------

1: ut: mgi1-8 |t:

MultiGigabitEthernet1: 1

MultiGigabitEthernet2: 1

MultiGigabitEthernet3: 1

MultiGigabitEthernet4: 1

MultiGigabitEthernet5: 1

MultiGigabitEthernet6: 1

MultiGigabitEthernet7: 1

MultiGigabitEthernet8: 1

------------------ Port Isolation ------------------

Port | Protected State

--------+-----------------

mgi1 |disabled

mgi2 |disabled

mgi3 |disabled

mgi4 |disabled

mgi5 |disabled

mgi6 |disabled

mgi7 |disabled

mgi8 |disabled

lag1 |disabled

lag2 |disabled

lag3 |disabled

lag4 |disabled

lag5 |disabled

lag6 |disabled

lag7 |disabled

lag8 |disabled

------------------ LAG Summary ------------------

Group ID | Ports

----------+----------------------------------------------

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

------------------ QoS ------------------

LP Trust Queue Weight

--- ------ ------ -----------------------------

0 0 0 1 1 1 1 1 1 1 1

1 0 0 1 1 1 1 1 1 1 1

2 0 0 1 1 1 1 1 1 1 1

3 0 0 1 1 1 1 1 1 1 1

4 0 0 1 1 1 1 1 1 1 1

5 0 0 1 1 1 1 1 1 1 1

6 0 0 1 1 1 1 1 1 1 1

7 0 0 1 1 1 1 1 1 1 1

------------------ Rate Limit ------------------

Port IGS State (Rate) EGS State (Rate)

------- -------------------- ---------------------

mgi1 disabled( 65536) disabled( 62496)

mgi2 disabled( 65536) disabled( 62496)

mgi3 disabled( 65536) disabled( 62496)

mgi4 disabled( 65536) disabled( 62496)

mgi5 disabled( 65536) disabled( 62496)

mgi6 disabled( 65536) disabled( 62496)

mgi7 disabled( 65536) disabled( 62496)

mgi8 disabled( 65536) disabled( 62496)

------------------ Cable Diagnostic ------------------

Port | Speed | Local pair | Pair length | Pair status

--------+--------+------------+-------------+---------------

mgi1 | auto | Pair A | 7.00 | Normal

Pair B | 7.00 | Normal

Pair C | 7.00 | Normal

Pair D | 7.00 | Normal

mgi2 | auto | Pair A | 0.71 | Normal

Pair B | 0.60 | Normal

Pair C | 0.52 | Normal

Pair D | 0.21 | Normal

mgi3 | auto | Pair A | 0.45 | Normal

Pair B | 0.32 | Normal

Pair C | 0.25 | Normal

Pair D | 0.53 | Normal

mgi4 | auto | Pair A | 0.71 | Normal

Pair B | 0.22 | Normal

Pair C | 0.53 | Normal

Pair D | 0.21 | Normal

mgi5 | auto | Pair A | 0.85 | Normal

Pair B | 0.35 | Normal

Pair C | 0.65 | Normal

Pair D | 0.21 | Normal

mgi6 | auto | Pair A | 0.72 | Normal

Pair B | 0.62 | Normal

Pair C | 0.22 | Normal

Pair D | 0.21 | Normal

mgi7 | auto | Pair A | 0.33 | Normal

Pair B | 0.21 | Normal

Pair C | 0.53 | Normal

Pair D | 0.21 | Normal

mgi8 | auto | Pair A | 0.73 | Normal

Pair B | 0.62 | Normal

Pair C | 0.55 | Normal

Pair D | 0.21 | Normal

------------------ Mirror ------------------

Session 1 Configuration

Mirrored source : Not Config

Destination port : Not Config

Session 2 Configuration

Mirrored source : Not Config

Destination port : Not Config

Session 3 Configuration

Mirrored source : Not Config

Destination port : Not Config

Session 4 Configuration

Mirrored source : Not Config

Destination port : Not Config

------------------ Optical Module ------------------

Port | Type | Media | Status (OE/LOS) | Nominal Bitrate (SFP) | Config

------+-------+--------+------------------+-----------------------+--------

------------------ SNMP ------------------

SNMP is enabled.

SNMP auth failed trap : Enable

SNMP linkUpDown trap : Enable

SNMP cold-start trap : Enable

SNMP warm-start trap : Enable

Commnunity Name Group Name View Access

-------------------- ------------------------------ ------------------------------ ------------

private all rw

public all ro

Total Entries: 2

Local SNMPV3 Engine id: 80006a9203002824129297

IP address Remote SNMP engineID

--------------------------------- -----------------------------------------------------------------

Total Entries: 0

Group Name Model Level ReadView WriteView NotifyView

------------------------------ ------ ------------ ------------------------------ ------------------------------ ------------------------------

Total Entries: 0

Server Community/User Name Notification Version Notification Type UDP Port Retries Timeout

---------------------------------------------------------------------------------------------------------------------

1.1.1.254 private v2c trap 162 -- --

Total Entries: 1

Total Entries: 0

View Name Subtree OID OID Mask View Type

--------------------------- -------------------------------------- ---------------------- ---------

all .1 all included

Total Entries: 1

------------------ SSH ------------------

SSH Server : enabled

Session Timeout : 10 (minutes)

History Count : 128

Password Retry : 3

Silent Time : 0 (seconds)

OpenSSL 1.0.2h 3 May 2016

------------------ Jumbo Frame ------------------

jumbo-frame: 1522

------------------ Process Memory ------------------

total(KB) used(KB) free(KB) shared(KB) buffer(KB) cache(KB)

--------------------+------------+------------+------------+------------+------------

Mem: 255208 68788 186420 0 0 0

-/+ buffers/cache: 68788 186420

Swap: 0 0 0

PID MEM(KB) COMMAND

1 724 init

2 0 kthreadd